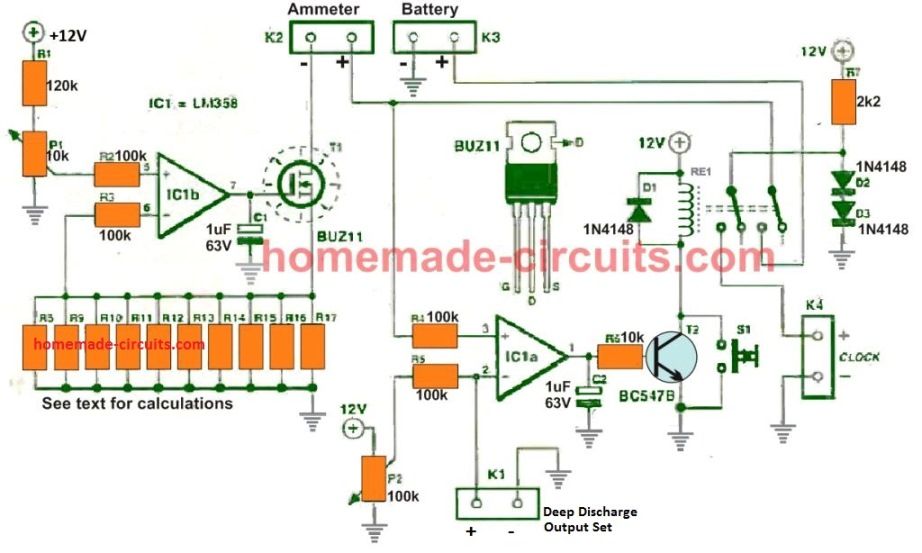

Le transistor à effet de champ (FET) est un appareil électronique dans lequel un champ électrique est utilisé pour réguler le flux de courant. Pour mettre en œuvre cela, une différence de potentiel est appliquée entre les bornes de grille et de source du dispositif, ce qui modifie la conductivité entre les bornes de drain et de source, provoquant le passage d'un courant contrôlé à travers ces bornes.

Les FET sont appelés transistors unipolaires parce que ceux-ci sont conçus pour fonctionner comme des dispositifs de type mono-opérateur. Vous trouverez différents types de transistors à effet de champ disponibles.

symbole

Les symboles graphiques des JFET à canal n et à canal p peuvent être visualisés dans les figures suivantes.

Vous pouvez clairement remarquer que les marques de flèche qui pointent vers l'intérieur pour que le périphérique à canal n indique la direction dans laquelle jeg(courant de grille) est censé circuler lorsque la jonction p-n était polarisée en direct.

Dans le cas d'un appareil à canal p, les conditions sont identiques à l'exception de la différence dans la direction du symbole de la flèche.

Différence entre FET et BJT

Le transistor à effet de champ (FET) est un dispositif à trois bornes conçu pour une large gamme d'applications de circuits qui complètent, à un niveau élevé, celles du transistor BJT.

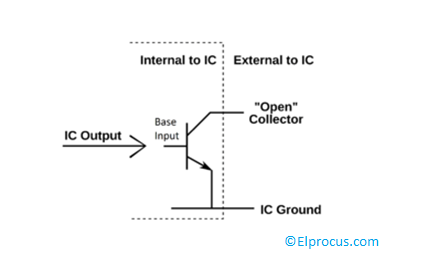

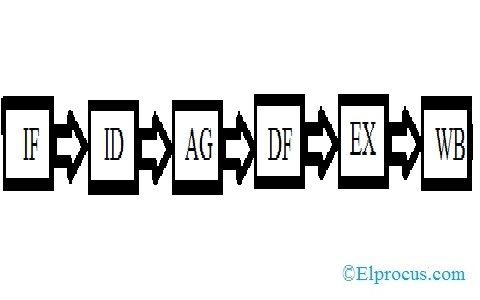

Bien que vous constatiez des écarts significatifs entre les BJT et les JFET, il existe en fait plusieurs caractéristiques d'appariement qui seront abordées dans les discussions suivantes. La principale distinction entre ces dispositifs est que BJT est un dispositif commandé en courant comme représenté sur la figure 5.1a, tandis que le transistor JFET est un dispositif commandé en tension comme indiqué sur la figure 5.1b.

En termes simples, le courant ICsur la figure 5.1a est une fonction immédiate du niveau de IB. Pour le FET, le courant I est fonction de la tension VGSdonné au circuit d'entrée comme illustré à la Fig. 5.1b.

Dans les deux cas, le courant du circuit de sortie sera régi par un paramètre du circuit d'entrée. Dans une situation, un niveau de courant et dans l'autre une tension appliquée.

Tout comme npn et pnp pour les transistors bipolaires, vous trouverez des transistors à effet de champ à canal n et à canal p. Mais, il faut se rappeler que le transistor BJT est un dispositif bipolaire le préfixe bi- indiquant que le niveau de conduction est fonction de deux porteurs de charge, des électrons et des trous.

Le FET en revanche est un appareil unipolaire cela dépend uniquement de la conduction d'électrons (canal n) ou de trou (canal p).

L'expression «effet de champ» peut être expliquée comme ceci: nous sommes tous conscients du pouvoir d'un aimant permanent pour attirer les limailles métalliques vers l'aimant sans aucun contact physique. Tout à fait de manière similaire à l'intérieur du FET, un champ électrique est créé par les charges existantes qui influencent le chemin de conduction du circuit de sortie sans avoir de contact direct entre les grandeurs de contrôle et contrôlées. L'une des caractéristiques les plus cruciales du FET est probablement sa haute impédance d'entrée.

D'une magnitude de 1 à plusieurs centaines de mégohms, il surpasse considérablement les plages de résistance d'entrée normales des configurations BJT, un attribut extrêmement important lors du développement de modèles d'amplificateurs linéaires à courant alternatif.

Cependant, le BJT porte une plus grande sensibilité aux variations du signal d'entrée. Cela signifie que le changement de courant de sortie est généralement beaucoup plus important pour les BJT que pour les FET pour la même quantité de changement de leurs tensions d'entrée.

Pour cette raison, les gains de tension alternative standard pour les amplificateurs BJT peuvent être beaucoup plus élevés par rapport aux FET.

De manière générale, les FET sont considérablement plus résistants thermiquement que les BJT, et ont souvent une structure de plus petite taille par rapport aux BJT, ce qui les rend spécifiquement adaptés à l'intégration en tant que circuit intégré (IC)chips.

Les caractéristiques structurelles de certains FET, en revanche, peuvent leur permettre d'être plus sensibles aux contacts physiques que les BJT.

Plus de relations BJT / JFET

- Pour un BJT VÊTRE= 0,7 V est le facteur important pour démarrer une analyse de sa configuration.

- De même, le paramètre Ig= 0 A est généralement la première chose à considérer pour l'analyse d'un circuit JFET.

- Pour la configuration BJT, jeBest souvent le premier facteur à déterminer.

- De même, pour le JFET, il s'agit généralement du VGS.

Dans cet article, nous nous concentrerons sur les JFET ou les transistors à effet de champ de jonction, dans le prochain article, nous discuterons du transistor à effet de champ à oxyde de métal semi-conducteur ou MOS-FET.

CONSTRUCTION ET CARACTÉRISTIQUES DES JFET

Comme nous l'avons appris plus tôt, un JFET a 3 pistes. L'un d'eux contrôle le flux de courant entre les deux autres.

Tout comme les BJT, dans les JFET également, le périphérique à canal n est utilisé plus en évidence que les homologues à canal p, car les périphériques n ont tendance à être plus efficaces et plus conviviaux que le périphérique p.

Dans la figure suivante, nous pouvons voir la structure de base ou la construction d'un JFET à canal n. Nous pouvons voir que la composition de type n forme le canal principal à travers les couches de type p.

La partie supérieure du canal de type n est reliée par un contact ohmique avec une borne nommée le drain (D), tandis que la section inférieure du même canal est également connectée par un contact ohmique avec une autre borne nommée la source (S).

Le couple de matériaux de type p est lié ensemble à la borne appelée grille (G). Essentiellement, nous constatons que les bornes de drain et de source sont reliées aux extrémités du canal de type n. La borne de grille est reliée à une paire de matériau à canal p.

Lorsqu'aucune tension n'est appliquée sur un jfet, ses deux jonctions p-n sont sans aucune condition de polarisation. Dans cette situation, il existe une région d'appauvrissement sur chaque jonction comme indiqué sur la figure ci-dessus, qui ressemble tout à fait à une région de diode p-n sans polarisation.

Analogie de l'eau

Les opérations de fonctionnement et de contrôle d'un JFET peuvent être comprises à travers l'analogie de l'eau suivante.

Ici, la pression d'eau peut être comparée à l'amplitude de la tension appliquée du drain vers la source.

Le flux d'eau peut être comparé au flux d'électrons. L'embouchure du robinet imite la borne de source du JFET, tandis que la partie supérieure du robinet où l'eau est forcée à entrer représente le drain du JFET.

Le bouton Tap agit comme le Gate du JFET. À l'aide d'un potentiel d'entrée, il contrôle le flux d'électrons (charge) du drain à la source, tout comme le bouton du robinet contrôle le débit d'eau sur l'ouverture de la bouche.

À partir de la structure JFET, nous pouvons voir que le drain et les bornes de la source sont aux extrémités opposées du canal n, et comme le terme est basé sur le flux d'électrons, nous pouvons écrire:

VGS= 0 V, VDSUne valeur positive

Sur la figure 5.4, nous pouvons voir une tension positive VDSappliqué à travers le canal n. Le terminal de porte est directement joint à la source pour créer une condition VGS= 0V. Cela permet à la porte et aux bornes de source d'être à un potentiel identique, et se traduit par une région d'appauvrissement d'extrémité inférieure de chaque matériau p, exactement comme nous le voyons dans le premier diagramme ci-dessus avec une condition sans polarisation.

Dès qu'une tension VDD(= VDS) est appliquée, les électrons sont attirés vers la borne de drain, générant le flux conventionnel de courant ID, comme indiqué sur la figure 5.4.

La direction du flux de la charge révèle que le drain et le courant de source sont égaux en grandeur (Iré= JeS). Selon les conditions décrites sur la figure 5.4, le flux de la charge semble tout à fait illimité et n'est affecté que par la résistance du canal n entre le drain et la source.

Vous pouvez observer que la région de déplétion est plus grande autour de la section supérieure des deux matériaux de type p. Cette différence de taille de la région est idéalement expliquée par la figure 5.5. Imaginons avoir une résistance uniforme dans le canal n, celle-ci pourrait être divisée en sections indiquées sur la figure 5.5.

Le courant jerépeut construire les plages de tension à travers le canal comme indiqué sur la même figure. En conséquence, la région supérieure du matériau de type p va être polarisée en inverse d'un niveau d'environ 1,5 V, la région inférieure étant simplement polarisée en inverse de 0,5 V.

Le point où la jonction p-n est polarisée en inverse le long de la totalité du canal donne lieu à un courant de grille de zéro ampère comme indiqué sur la même figure. Cette caractéristique qui conduit à jeg= 0 A est une caractéristique importante du JFET.

Comme VDSle potentiel est augmenté de 0 à quelques volts, le courant augmente selon la loi d'Ohm et le tracé de Iréligne 5DSpeut ressembler à ce que montre la Fig. 5.6.

La rectitude comparative du tracé montre que pour les régions de faible valeur de VDS, la résistance est essentiellement uniforme. Comme VDSmonte et s'approche d'un niveau connu sous le nom de VP sur la figure 5.6, les régions d'appauvrissement s'élargissent comme indiqué sur la figure 5.4.

Il en résulte un abaissement apparent de la largeur du canal. Le chemin de conduction diminué conduit à l'augmentation de la résistance donnant naissance à la courbe de la figure 5.6.

Plus la courbe est horizontale, plus la résistance est élevée, ce qui indique que la résistance se dirige vers des ohms «infinis» dans la région horizontale. Lorsque VDSaugmente dans une mesure où il semblerait que les deux régions d'appauvrissement puissent «entrer en contact» comme le montre la figure 5.7, donne lieu à une situation connue sous le nom de pincement.

Le montant par lequel VDSdéveloppe cette situation s'appelle le pincement tension et il est symbolisé par VPcomme présenté à la Fig. 5.6. En général, le mot pincement est trompeur car il implique le courant Iréest «pincé» et tombe à 0 A. Comme le montre la figure 5.6, cela ne semble guère évident dans ce cas. jeréconserve un niveau de saturation caractérisé par IDSSdans la Fig. 5.6.

La vérité est qu'un très petit canal continue d'exister, avec un courant de concentration significativement élevée.

Le moment où l'ID ne tombe pas à pincement et préserve le niveau de saturation comme indiqué sur la Fig.5.6 est confirmé par la preuve suivante:

Puisqu'il n'y a pas de courant de drain, élimine la possibilité de divers niveaux de potentiel à travers le matériau à canal n pour déterminer les quantités variables de polarisation inverse le long de la jonction p-n. Le résultat final étant la perte de la distribution de la région d'épuisement qui a déclenché pincement commencer avec.

À mesure que nous augmentons VDSau-dessus de VP, la région de contact étroit où les deux régions d'appauvrissement se rencontreront augmente en longueur le long du canal. Cependant, le niveau d'identification reste essentiellement inchangé.

Ainsi le moment VDSest supérieur à Vp, le JFET acquiert les caractéristiques de la source de courant.

Comme le montre la figure 5.8, le courant dans un JFET est déterminé à Iré= JeDSS, mais tension VDSsupérieur à VP est établi par la charge connectée.

La sélection de la notation IDSS est basée sur le fait que c'est le courant Drain to Source ayant une liaison court-circuitée entre la porte et la source.

Une enquête plus approfondie nous donne l'évaluation suivante:

jeDSSest le courant de drain le plus élevé pour un JFET et est établi par les conditions VGS= 0 V et VDS> | VP |.

Notez que sur la Fig.5,6 VGSest 0V pour l'étirement complet de la courbe. Dans les sections suivantes, nous apprendrons comment les attributs de la Fig 5.6 sont influencés par le niveau de VGSest varié.

VGS <0V

La volatilité appliquée à travers la porte et la source est signifiée comme VGS, qui est responsable du contrôle des opérations JFET.

Si nous prenons l'exemple d'un BJT, tout comme les courbes de ICvs VCEsont déterminés pour différents niveaux de IB, de même les courbes de Irévs VDSpour différents niveaux de VGSpeut être créé pour un homologue JFET.

Pour cela, la borne de grille est réglée à un potentiel inférieur continu en dessous du niveau du potentiel source.

En se référant à la Fig.5.9 ci-dessous, un -1V est appliqué à travers les bornes porte / source pour un V réduitDSniveau.

L'objectif du biais potentiel négatif VGSest de développer des régions d'épuisement ressemblant à la situation de VGS= 0, mais à V significativement réduitDS.

Cela amène la porte à atteindre un point de saturation avec des niveaux inférieurs de VDScomme indiqué sur la Fig.5.10 (VGS= -1 V).

Le niveau de saturation correspondant pour Irépeut être trouvée réduite et continue en fait à diminuer à mesure que VGSest rendu plus négatif.

Vous pouvez voir clairement sur la figure 5.10 comment la tension de pincement continue à chuter avec une forme parabolique comme VGSdevient de plus en plus négatif.

Enfin, quand VGS= -Vp, il devient suffisamment négatif pour établir un niveau de saturation qui est finalement de 0 mA. À ce niveau, le JFET est complètement «désactivé».

Le niveau de VGSce qui me faitrépour atteindre 0 mA est caractérisé par VGS= VP, où VPest une tension négative pour les appareils à canal n et une tension positive pour les JFET à canal p.

Généralement, vous pouvez trouver la plupart des fiches techniques JFET montrant pincement tension spécifiée en VGS (désactivé)au lieu de VP.

La zone sur le côté droit du lieu de pincement sur la figure ci-dessus est l'endroit classiquement utilisé dans les amplificateurs linéaires pour obtenir un signal sans distorsion. Cette région est généralement appelée région d'amplification à courant constant, saturation ou linéaire.

Résistance contrôlée en tension

La zone qui se trouve sur le côté gauche du locus de pincement sur la même figure est appelée région ohmique ou région de résistance contrôlée en tension.

Dans cette région, le dispositif peut en fait fonctionner comme une résistance variable (par exemple dans une application de contrôle automatique de gain), sa résistance étant commandée par le potentiel grille / source appliqué.

Vous pouvez voir que la pente de chacune des courbes qui signifie également la résistance drain / source du JFET pour VDS

Au fur et à mesure que nous augmentons le VGS avec un potentiel négatif, la pente de chaque courbe devient de plus en plus horizontale, présentant des niveaux de résistance proportionnellement croissants.

Nous pouvons obtenir une bonne approximation initiale du niveau de la résistance par rapport à la tension VGS, grâce à l'équation suivante.

P-Channel JFET fonctionnant

La disposition interne et la construction d'un JFET à canal p est exactement identique à son homologue à canal n, sauf que les régions de matériaux de type p et n sont inversées, comme indiqué ci-dessous:

Les directions du flux de courant peuvent également être considérées comme inversées, ainsi que les polarités réelles des tensions VGS et VDS. Dans le cas d'un JFET à canal p, le canal sera contraint en réponse à l'augmentation du potentiel positif à travers la porte / source.

La notation avec un double indice pour le VDSdonnera lieu à une tension négative pour VDS, comme indiqué sur les caractéristiques de la figure 5.12. Ici, vous pouvez trouver jeDSSà 6 mA, tandis qu'une tension de pincement à VGS= + 6V.

S'il vous plaît ne vous laissez pas perplexe en raison de la présence de vous signe moins pour le VDS. Cela indique simplement que la source porte un potentiel plus élevé que le drain.

Vous pouvez voir que les courbes pour V élevéDSles niveaux montent brusquement à des valeurs qui semblent illimitées. La montée indiquée qui est verticale symbolise une situation de claquage, ce qui signifie que le courant traversant le dispositif de canal est entièrement contrôlé par le circuit externe à ce moment.

Bien que cela ne soit pas apparent sur la figure 5.10 pour un dispositif à canal n, cela peut être une possibilité sous une tension suffisamment élevée.

Cette région peut être éliminée si le VDS (max)est noté sur la fiche technique de l'appareil, et l'appareil est configuré de telle sorte que le V réelDSla valeur est inférieure à cette valeur notée pour tout VGS.

Précédent: 5 meilleurs circuits d'amplification de 40 watts explorés Prochaine: Fiche technique 2N3055, brochage, circuits d'application