De nos jours, les protocoles jouent un rôle essentiel dans la conception de système embarqué . Sans passer aux protocoles, si vous souhaitez étendre les fonctionnalités périphériques du microcontrôleur, la complexité et la consommation d'énergie vont augmenter. Il existe différents types de protocoles de bus disponibles tels que USART, SPI, CAN, Protocole de bus I2C , etc., qui sont utilisés pour transférer les données entre deux systèmes.

Protocole I2C

Qu'est-ce que le bus I2C?

La transmission et la réception des informations entre deux ou plus de deux appareils nécessitent un chemin de communication appelé système de bus. Un bus I2C est un bus série bidirectionnel à deux fils qui est utilisé pour transporter les données entre les circuits intégrés. L'I2C signifie «Inter Integrated Circuit». Il a été introduit pour la première fois par les semi-conducteurs Philips en 1982. Le bus I2C se compose de trois vitesses de transfert de données telles que standard, mode rapide et mode haute vitesse. Le bus I2C prend en charge les périphériques d'espace d'adressage 7 bits et 10 bits et son fonctionnement diffère avec les basses tensions.

Protocole de bus I2c

Lignes de signal I2C

Lignes de signal I2C

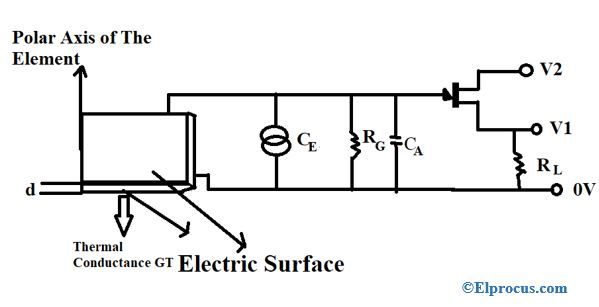

L'I2C est un protocole de bus série composé de deux lignes de signaux telles que des lignes SCL et SDL qui sont utilisées pour communiquer avec les appareils. Le SCL est synonyme de «ligne d'horloge série» et ce signal est toujours piloté par le «dispositif maître». Le SDL signifie «ligne de données série», et ce signal est piloté soit par le maître, soit par les périphériques I2C. Ces deux lignes SCL et SDL sont dans un état de drain ouvert lorsqu'il n'y a pas de transfert entre les périphériques I2C.

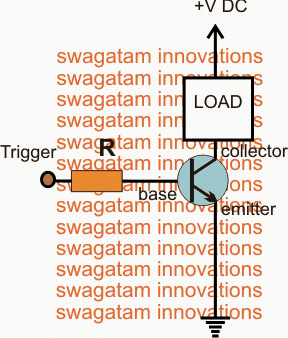

Sorties Open-Drain

Le drain ouvert est le concept pour transistor FET dans lequel la borne de drain du transistor est à l'état ouvert. Les broches SDL et SCL du dispositif maître sont conçues avec les transistors à l'état ouvert, de sorte que le transfert de données n'est possible que lorsque ces transistors sont conduits. Par conséquent, ces lignes ou bornes de drain sont connectées à des résistances de rappel à VCC pour le mode de conduction.

Interfaces I2C

De nombreux les appareils esclaves sont interfacés avec le microcontrôleur à l'aide du bus I2C via IC de décalage de niveau I2C pour transférer les informations entre eux. Le protocole I2C permet de connecter un maximum de 128 appareils qui sont tous connectés pour communiquer avec les lignes SCL et SDL de l'unité maître ainsi qu'avec les appareils esclaves. Il prend en charge la communication Multimaster, ce qui signifie que deux maîtres sont utilisés pour communiquer les périphériques externes.

Taux de transfert de données I2C

Le protocole I2C exploite trois modes tels que: le mode rapide, le mode haute vitesse et le mode standard dans lequel la vitesse de données en mode standard varie de 0 Hz à 100 Hz, et les données en mode rapide peuvent être transférées avec une vitesse de 0 Hz à 400 KHz et le mode haute vitesse avec 10 KHz à 100 KHz. Les données à 9 bits sont envoyées pour chaque transfert dans lequel 8 bits sont envoyés par l'émetteur MSB à LSB, et le 9e bit est un bit d'accusé de réception envoyé par le récepteur.

Taux de transfert de données I2C

Communication I2C

Le protocole de bus I2C est le plus couramment utilisé dans la communication maître et esclave dans laquelle le maître est appelé «microcontrôleur», et l'esclave est appelé d'autres dispositifs tels que ADC, EEPROM, DAC et des dispositifs similaires dans le système embarqué. Le nombre d'appareils esclaves est connecté au dispositif maître à l'aide du bus I2C, chaque esclave étant constitué d'une adresse unique pour le communiquer. Les étapes suivantes sont utilisées pour communiquer l'appareil maître à l'esclave:

Étape 1: Tout d'abord, le dispositif maître émet une condition de démarrage pour informer tous les dispositifs esclaves afin qu'ils écoutent sur la ligne de données série.

Étape 2: L’équipement maître envoie l’adresse de l’équipement esclave cible, qui est comparée aux adresses de tous les équipements esclaves connectés aux lignes SCL et SDL. Si une adresse correspond, ce périphérique est sélectionné et tous les autres périphériques sont déconnectés des lignes SCL et SDL.

Étape 3: Le dispositif esclave avec une adresse correspondante reçue du maître, répond par un acquittement au maître, après quoi la communication est établie entre les dispositifs maître et esclave sur le bus de données.

Étape 4: Le maître et l'esclave reçoivent et transmettent les données selon que la communication est en lecture ou en écriture.

Étape 5: Ensuite, le maître peut transmettre 8 bits de données au récepteur qui répond par un acquittement de 1 bit.

Tutoriel I2C

La transmission et la réception des informations pas à pas en série par rapport aux impulsions d'horloge est appelée protocole I2C. Il s'agit d'un protocole inter-système et à courte distance, ce qui signifie qu'il est utilisé dans la carte de circuit imprimé pour communiquer les dispositifs maître et esclave.

Principes de base du protocole I2C

En général, le système de bus I2C se compose de deux fils qui sont utilisés facilement pour étendre les fonctionnalités périphériques d'entrée et de sortie telles que ADC, EEROM et RTC, et autres composants de base faire un système dont la complexité est bien moindre.

Exemple: Puisque le microcontrôleur 8051 n'a pas d'ADC intégré - donc, si nous voulons interfacer des capteurs analogiques avec le microcontrôleur 8051 - nous devons utiliser des dispositifs ADC tels que ADC0804-1 canal ADC, ADC0808- 8 canaux ADC, etc. En utilisant ces ADC, nous pouvons interfacer les capteurs analogiques avec le microcontrôleur.

Sans utiliser le protocole pour étendre les fonctionnalités d'E / S d'un microcontrôleur ou d'un processeur, nous pouvons passer au 8255 ICit 8 broches. Le Le microcontrôleur 8051 est un microcontrôleur à 40 broches en utilisant le 8255 IC, nous pouvons étendre les ports 3-I / O avec 8 broches dans chaque port. En utilisant tous les appareils tels que RTC, ADC, EEPROM, minuteries, etc. - pour étendre les circuits périphériques - la complexité, le coût, la consommation d'énergie et la taille du produit sont également augmentés.

Pour surmonter ce problème, le concept de protocole entre en jeu pour réduire la complexité matérielle et la consommation d'énergie. Nous pouvons étendre plus de fonctionnalités, telles que les périphériques I / 0, ADC, T / C et les périphériques de mémoire jusqu'à 128 périphériques en utilisant ce protocole I2C.

Terminologie utilisée dans les protocoles I2C

Émetteur: L'appareil qui envoie des données au bus est appelé émetteur.

Destinataire: L'appareil qui reçoit les données du bus est appelé un récepteur.

Maître: L'appareil qui lance les transferts pour générer des signaux d'horloge et terminer un transfert est appelé un maître.

Trimer: L'appareil adressé par un maître est appelé un esclave.

Multimaster: Plus d'un maître peut tenter de contrôler le bus en même temps sans altérer le message est appelé un multimaître.

Arbitrage: Procédure garantissant que, si plusieurs maîtres tentent simultanément de contrôler le bus, un seul est autorisé à le faire, le message gagnant n'est pas corrompu.

Synchronisation: La procédure pour synchroniser les singles d'horloge de deux appareils ou plus est appelée synchronisation.

Séquence des commandes de base I2C

- Condition de bit de démarrage

- Condition de bit d'arrêt

- Condition d'acquittement

- Opération d'écriture de maître à esclave

- Lire l'opération esclave sur maître

Condition de bit de démarrage et d'arrêt

Lorsque le maître (microcontrôleur) souhaite parler à un appareil esclave (par exemple ADC), il commence la communication en émettant une condition de démarrage sur le bus I2C, puis émet une condition d'arrêt. Les niveaux logiques de démarrage et d'arrêt I2C sont indiqués sur la figure.

La condition de démarrage I2C se définit comme une transition de haut en bas de la ligne SDA alors que la ligne SCL est haute. Une condition d'arrêt I2C se produit lorsque la ligne SDA bascule de bas en haut alors que la ligne SCL est haute.

Le maître I2C génère toujours les conditions S et P. Une fois que le maître I2C initie une condition START, le bus I2c est considéré comme étant à l'état occupé.

Condition de bit de démarrage et d'arrêt

Programmation:

CONDITIONS DE DÉBUT:

sbit SDA = P1 ^ 7 // initialise les broches SDA et SCL du microcontrôleur //

sbit SCL = P1 ^ 6

délai d'annulation (int non signé)

void main ()

{

SDA = 1 // traitement des données //

SCL = 1 // l'horloge est haute //

retard()

SDA = 0 // a envoyé les données //

retard()

SCL = 0 // le signal d'horloge est bas //

}

Délai d'annulation (int p)

{

unsignedinta, b

Pour (a = 0a<255a++) //delay function//

Pour (b = 0b

Condition d'arrêt:

void main ()

{

SDA = 0 // Arrêter le traitement des données //

SCL = 1 // l'horloge est haute //

retard()

SDA = 1 // Arrêté //

retard()

SCL = 0 // le signal d'horloge est bas //

}

Délai d'annulation (int p)

{

unsignedinta, b

Pour (a = 0a<255a++) //delay function//

Pour (b = 0b

Condition d'acquittement (ACK) et de non accusé de réception (NCK)

Chaque octet transmis sur le bus I2C est suivi d'une condition d'acquittement du récepteur, ce qui signifie que, après que le maître a tiré SCL bas pour terminer la transmission de 8 bits, le SDA sera tiré bas par le récepteur vers le maître. Si, après la transmission du récepteur ne tire pas, la ligne SDA LOW est considérée comme une condition NCK.

Accusé de réception (ACK)

Programmation

Reconnaissance

void main ()

{

SDA = 0 // La ligne SDA passe au niveau bas //

SCL = 1 // l'horloge est de haut en bas //

retard (100)

SCL = 0

}

Pas de reconnaissance:

void main ()

{

SDA = 1 // La ligne SDA passe à haut //

SCL = 1 // l'horloge est de haut en bas //

retard (100)

SCL = 0

}

Opération d'écriture maître vers esclave

Le protocole I2C transfère les données sous forme de paquets ou d'octets. Chaque octet est suivi d'un bit d'acquittement.

Format de transfert de données

Format de transfert de données

Début: Principalement, la séquence de transfert de données initiée par le maître générant la condition de démarrage.

Adresse 7 bits: Ensuite, le maître envoie l'adresse de l'esclave dans deux formats 8 bits au lieu d'une seule adresse 16 bits.

R / W: Si le bit de lecture et d'écriture est haut, l'opération d'écriture est exécutée.

HÉLAS: Si l'opération d'écriture est effectuée dans le dispositif esclave, le récepteur envoie alors l'ACK 1 bit au microcontrôleur.

Arrêter: Une fois l'opération d'écriture terminée dans le dispositif esclave, le microcontrôleur envoie la condition d'arrêt au dispositif esclave.

Programmation

Opération d'écriture

voidwrite (caractère non signé d)

{

Caractère non signé k, j = 0x80

Pour (k = 0k<8k++)

{

SDA=(d&j)

J=j>>1

SCL = 1

retard (4)

SCL = 0

}

SDA = 1

SCL = 1

retard (2)

c = SDA

retard (2)

SCL = 0

}

Opération de lecture maître à esclave

Les données sont lues à partir du périphérique esclave sous forme de bit ou d'octets - lisez d'abord le bit le plus significatif et le dernier le bit le moins significatif.

Le format de lecture des données

Format de lecture des données

Début: Principalement, la séquence de transfert de données est initiée par le maître générant la condition de démarrage.

Adresse 7 bits: Ensuite, le maître envoie l'adresse de l'esclave dans deux formats 8 bits au lieu d'une seule adresse 16 bits.

R / W: Si le bit de lecture et d'écriture est bas, l'opération de lecture est exécutée.

HÉLAS: Si l'opération d'écriture est effectuée dans le dispositif esclave, le récepteur envoie alors l'ACK 1 bit au microcontrôleur.

Arrêter: Une fois l'opération d'écriture terminée dans le dispositif esclave, le microcontrôleur envoie la condition d'arrêt au dispositif esclave.

Programmation

Lecture nulle ()

{

Caractère non signé j, z = 0x00, q = 0x80

SDA = 1

pour (j = 0j<8j++)

{

SCL = 1

retard (100)

drapeau = SDA

si (drapeau == 1)

q)

q = q >> 1

retard (100)

SCL = 0

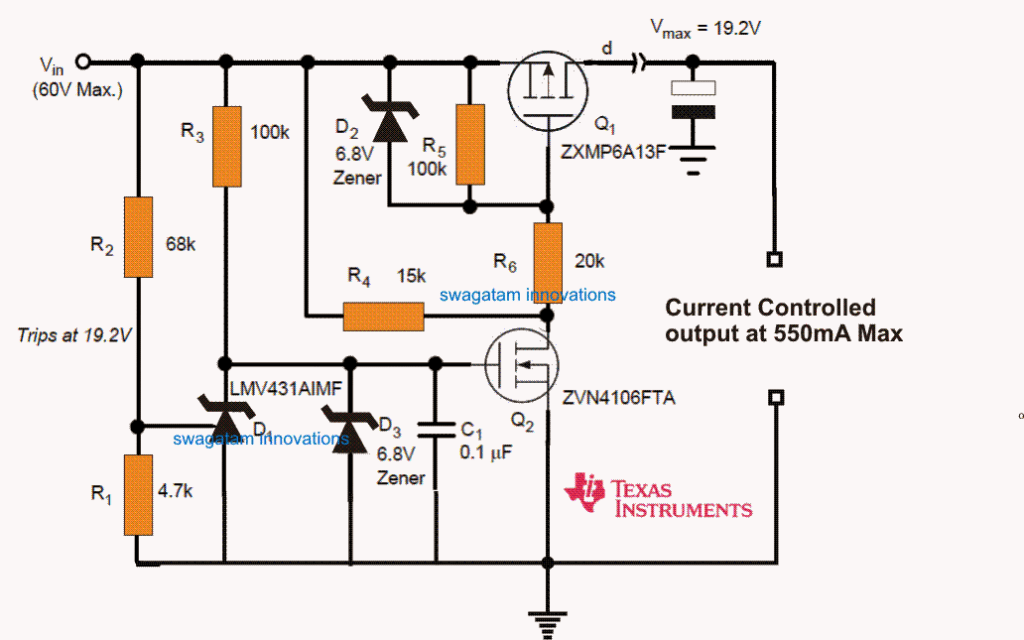

Exemple pratique d'interfaçage ADC avec le microcontrôleur 8051

L'ADC est un appareil qui est utilisé pour convertir les données analogiques sous forme de numérique et numérique en analogique. Le microcontrôleur 8051 ne dispose pas d'un ADC intégré, nous devons donc l'ajouter en externe via le protocole I2C. Le PCF8591 est basé sur I2C analogique vers numérique et convertisseur numérique-analogique. Cet appareil peut prendre en charge un maximum de 4 canaux d'entrée analogiques avec des tensions de 2,5 à 6 V.

Sorties analogiques

Les sorties analogiques se présentent sous la forme de tensions. Par exemple, un capteur analogique 5v donne une logique de sortie de 0,01v à 5v.

La valeur numérique maximale de 5v est = 256.

La valeur de 2,5 V est = 123 selon la valeur de tension maximale.

La formule de la sortie analogique est:

La formule des sorties numériques:

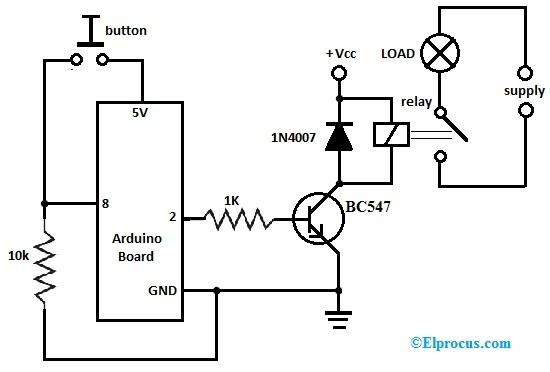

Interfaçage ADC avec le microcontrôleur 8051

La figure ci-dessus montre le transfert de données à l'aide du protocole I2C du dispositif ADC vers le microcontrôleur 8051. Les broches ADC de SCL et SDA sont connectées aux broches 1.7 et 1.6 du microcontrôleur pour établir la communication entre elles. Lorsque le capteur donne des valeurs analogiques à l'ADC, il se convertit en numérique et transfère les données au microcontrôleur via le protocole I2C.

Il s'agit du tutoriel sur le protocole de bus I2C avec les programmes appropriés. Nous espérons que le contenu donné vous donne un concept pratique d'interfaçage de plusieurs appareils avec des microcontrôleurs en utilisant la communication I2C. En cas de doute sur la procédure d'interfaçage de ce protocole, vous pouvez nous joindre en commentant ci-dessous.