JTAG (Joint Test Action Group) est une norme IEEE 1149.1 bien établie qui a été développée en 1980 pour résoudre les problèmes de fabrication survenus dans les cartes électroniques ou cartes de circuits imprimés . Cette technologie est utilisée pour fournir suffisamment d'accès aux tests pour chaque carte complexe lorsque l'accès aux tests diminuait. Ainsi, la technologie de balayage périphérique a été lancée et la norme JTAG ou Spécification JTAG est établi. La complexité de l'électronique a augmenté de jour en jour, de sorte que la spécification JTAG est devenue le format de test accepté pour tester les unités électroniques complexes et compactes. Cet article donne un aperçu d'un JTAG protocole – travailler avec des applications.

Qu'est-ce que JTAG ?

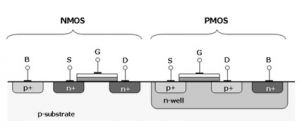

Le nom donné au port d'accès de test standard IEEE 1149.1 ainsi qu'à l'architecture Boundary-Scan est connu sous le nom de JTAG (Joint Test Action Group). Cette architecture d'analyse périphérique est principalement utilisée dans les ordinateurs processeurs car le premier processeur avec JTAG a été publié par Intel. Cette norme IEEE définit simplement comment le circuit d'un ordinateur est testé pour confirmer s'il fonctionne correctement après la procédure de fabrication. Sur les circuits imprimés, des tests sont effectués pour vérifier les joints de soudure.

Joint Test Action Group fournit une vue des broches pour les testeurs avec chaque pad IC, ce qui aide à identifier les défauts dans une carte de circuit imprimé. Une fois ce protocole interfacé à une puce, celui-ci peut attacher une sonde à la puce en permettant à un développeur de contrôler la puce ainsi que ses connexions avec d'autres puces. L'interface avec le groupe Joint Test Action peut également être utilisée par les développeurs pour copier le micrologiciel dans la mémoire non volatile d'un appareil électronique.

Configuration/brochage

Le groupe d'action de test conjoint comprend 20 broches où chaque broche et sa fonction sont décrites ci-dessous.

Broche1 (VTréf) : Il s'agit de la broche de tension de référence cible qui est utilisée pour se connecter à l'alimentation principale de la cible qui va de 1,5 à 5,0 VCC.

Pin2 (Valimentation): Il s'agit de la tension d'alimentation cible qui est utilisée pour connecter l'alimentation en tension principale de la cible 1,5 VCC à 5,0 VCC.

Broche3 (nTRST) : Il s'agit d'une broche de réinitialisation de test utilisée pour réinitialiser la machine d'état du contrôleur TAP.

Broches (4, 6, 8, 10, 12, 14, 16, 18 & 20): Ce sont des broches GND communes.

Broche5 (TDI): Ce sont les données de test dans la broche. Ces données sont transférées vers l'appareil cible. Cette broche doit être tirée vers le haut dans une condition définie sur la carte cible.

Broche7 (TMS): Il s'agit de la broche d'état du mode test qui est tirée pour déterminer l'état suivant de la machine d'état du contrôleur TAP.

Broche 9 (TCK): Il s'agit d'une broche d'horloge de test qui synchronise les opérations de la machine d'état interne dans le contrôleur TAP.

Broche11 (RTCK): Il s'agit de la broche Input Return TCK qui est utilisée dans les appareils prenant en charge l'horloge adaptative.

Broche 13 (TDO): Il s'agit de la broche Test Data Out, de sorte que les données sont déplacées de l'appareil cible vers le Flyswatter.

Broche 15 (nSRST) : Il s'agit de la broche de réinitialisation du système cible qui est connectée au signal de réinitialisation principal de la cible.

Broches 17 et 19 (NC) : Ce ne sont pas des broches connectées.

Travail JTAG

L'utilisation originale du JTAG est pour les tests aux limites. Ici, est une simple carte de circuit imprimé comprenant deux circuits intégrés comme CPU & FPGA . Une carte typique peut inclure de nombreux circuits intégrés. En général, les circuits intégrés comprennent de nombreuses broches qui sont connectées conjointement avec de nombreuses connexions. Ici, dans le schéma suivant, seules quatre connexions sont représentées.

Donc, si vous concevez de nombreuses cartes où chaque carte a des milliers de connexions. En cela, il y a quelques mauvaises planches. Nous devons donc vérifier quelle carte fonctionne et laquelle ne fonctionne pas. Pour cela, le Joint Test Action Group a été conçu.

Ce protocole peut utiliser les broches de contrôle de toutes les puces mais dans le schéma suivant, le Joint Test Action Group va créer toutes les broches de sortie du CPU et toutes les broches d'entrée du FPGA. Après cela, en transmettant une certaine quantité de données à partir des broches du CPU et en lisant les valeurs des broches du FPGA, JTAG déclare que les connexions de la carte PCB sont correctes.

En fait, le Joint Test Action Group comprend quatre signaux logiques TDI, TDO, TMS et TCK. Et ces signaux doivent être connectés d'une manière particulière. Au début, TMS et TCK sont connectés en parallèle à tous les circuits intégrés de JTAG.

Après cela, le TDI et le TDO sont connectés pour former une chaîne. Comme vous pouvez le constater, chaque circuit intégré compatible JTAG comprend 4 broches qui sont utilisées pour JTAG où 3 broches sont des entrées et la 4ème broche est une sortie. La cinquième broche comme TRST est facultative. Habituellement, les broches JTAG ne sont pas partagées à d'autres fins.

En utilisant le groupe d'action de test conjoint, tous les circuits intégrés utilisent des tests de limite dont la raison d'origine est créée par JTAG. À l'heure actuelle, l'utilisation de ce protocole a été étendue pour permettre différentes choses comme la configuration des FPGA et après cela, JTAG est utilisé dans le cœur du FPGA à des fins de débogage.

Architecture JTAG

L'architecture JTAG est illustrée ci-dessous. Dans cette architecture, tous les signaux entre la logique centrale de l'appareil et les broches sont interrompus par un chemin de balayage série appelé BSR ou Boundary Scan Register. Ce BSR comprend diverses « cellules » de balayage périphérique. Généralement, ces cellules de balayage périphérique ne sont pas visibles, mais elles peuvent être utilisées pour définir ou lire des valeurs en mode test à partir des broches de l'appareil.

L'interface JTAG appelée TAP ou Test Access Port utilise différents signaux pour prendre en charge l'opération de balayage périphérique comme TCK, TMS, TDI, TDO et TRST.

- Le signal TCK ou Test Clock synchronise simplement les opérations internes d'une machine d'état.

- Le signal TMS ou Test Mode Select est échantillonné sur le front montant d'un signal d'horloge de test pour décider de l'état suivant.

- Le signal TDI ou Test Data In signifie les données décalées dans le dispositif de test, sinon la logique de programmation. Une fois que la machine à états interne est dans le bon état, elle est échantillonnée au front croissant de TCK.

- Le signal TDO ou Test Data Out signifie les données décalées du dispositif de test, sinon la logique de programmation. Une fois que la machine à états interne est dans le bon état, elle est valide sur le front décroissant de TCK

- TRST ou Test Reset est une broche facultative utilisée pour réinitialiser la machine d'état du contrôleur TAP.

Contrôleur TAP

Le point d'accès de test dans l'architecture de JTAG est composé d'un contrôleur TAP, d'un registre d'instructions et de registres de données de test. Ce contrôleur comprend la machine d'état de test qui est responsable de la lecture des signaux TMS et TCK. Ici, la broche i/p de données est simplement utilisée pour charger des données dans les cellules limites entre le cœur du circuit intégré et les broches physiques, et également pour charger des données dans l'un des registres de données ou dans le registre d'instructions. La broche o/p de données est utilisée pour lire des données à partir des registres ou des cellules limites.

La machine d'état du contrôleur TAP est contrôlée par le TMS et elle est cadencée par TCK. La machine d'état utilise deux chemins pour signifier deux modes différents comme le mode instruction et le mode données.

Registres

Deux types de registres sont disponibles dans le balayage périphérique. Chaque appareil conforme comprend au moins deux registres de données et un registre d'instructions.

Registre des instructions

Le registre d'instruction est utilisé pour contenir l'instruction en cours. Ainsi, ses données sont utilisées par le contrôleur TAP pour décider quoi exécuter avec les signaux obtenus. Le plus souvent, les données du registre d'instructions décriront vers lequel des registres de données les signaux doivent être passés.

Registres de données

Les registres de données sont disponibles en trois types : le BSR (Boundary Scan Register), le BYPASS et le registre ID CODES. Et aussi, d'autres registres de données peuvent être là, mais ils ne sont pas nécessaires en tant qu'élément de la norme JTAG.

Registre de balayage des limites (BSR)

BSR est le principal registre de données de test utilisé pour déplacer les données depuis et vers les broches d'E/S du périphérique.

CONTOURNE

Bypass est un registre à bit unique utilisé pour transmettre des données de TDI à TDO. Ainsi, il permet de tester des appareils supplémentaires dans un circuit avec un minimum de surcharge.

CODES D'IDENTIFICATION

Ce type de registre de données comprend le code d'identification ainsi que le numéro de révision de l'appareil. Ces données permettent donc à l'appareil d'être connecté à son fichier BSDL (Boundary Scan Description Language). Ce fichier comprenait les détails de configuration de Boundary Scan pour le périphérique.

Le fonctionnement de JTAG est, initialement, le mode d'instruction est choisi où l'un des états de ce mode 'chemin' permet à l'opérateur de chronométrer une instruction par TDI. Après cela, la machine à états se développe jusqu'à ce qu'elle se réorganise. L'étape suivante pour la plupart des instructions consiste à choisir le mode de données. Ainsi, dans ce mode, les données sont chargées via TDI pour être lues à partir de TDO. Pour TDI et TDO, les chemins de données seront organisés conformément à l'instruction qui a été cadencée. Une fois l'opération de lecture/écriture terminée, la machine d'état se développe à nouveau vers l'état de réinitialisation.

Différence entre JTAG et UART

La différence entre JTAG et UART comprend les éléments suivants.

| JTAG |

UART |

| Le terme « JTAG » signifie Joint Test Action Group. | Le terme ' UART » signifie Universal Asynchronous Receiver/Transmitter. |

| C'est une interface synchrone qui utilise du matériel intégré pour programmer le flash . | UART est une interface asynchrone qui utilise un chargeur de démarrage qui s'exécute dans la mémoire. |

| Il s'agit d'un ensemble de ports de test utilisés pour le débogage mais qui peuvent également être utilisés pour programmer le micrologiciel (ce qui est couramment fait).

|

UART est un type de puce qui contrôle les communications vers et depuis un appareil, tel qu'un microcontrôleur, une ROM, une RAM, etc. La plupart du temps, c'est une connexion série qui nous permet de communiquer avec un appareil. |

| Ceux-ci sont disponibles en quatre types TDI, TDO, TCK, TMS et TRST. | Ceux-ci sont disponibles en deux types UART muet et FIFO UART. |

| Joint Test Action Group est un protocole de programmation série ou d'accès aux données qui est utilisé dans l'interfaçage des microcontrôleurs et des dispositifs associés. | Un UART est un type de puce, sinon un sous-composant de microcontrôleur qui est utilisé pour fournir le matériel permettant de générer un flux série asynchrone comme RS-232/RS-485. |

| Les composants JTAG sont des processeurs, des FPGA, CPLD , etc. | Les composants UART sont le générateur CLK, les registres à décalage d'E/S, les tampons de transmission ou de réception, le tampon de bus de données système, la logique de contrôle de lecture ou d'écriture, etc. |

Analyseur de protocole JTAG

L'analyseur de protocole JTAG comme PGY-JTAG-EX-PD est un type d'analyseur de protocole comprenant certaines fonctionnalités pour capturer et déboguer la communication entre l'hôte et la conception testée. Ce type d'analyseur est l'instrument principal qui permet aux ingénieurs de test et de conception de tester les conceptions particulières de JTAG pour ses spécifications en organisant le PGY-JTAG-EX-PD comme maître ou esclave pour générer du trafic JTAG et décoder les paquets de décodage du Protocole du groupe d'action sur les tests conjoints.

Fonctionnalités

Les caractéristiques de l'analyseur de protocole JTAG sont les suivantes.

- Il prend en charge jusqu'à 25 MH de fréquences JTAG.

- Il génère simultanément du trafic JTAG et un décodage de protocole pour le bus.

- Il a la capacité de maître JTAG.

- Vitesses de données JTAG variables et cycle de service.

- Délais TDI et TCK définis par l'utilisateur.

- Interface USB 2.0 ou 3.0 de l'ordinateur hôte.

- Analyse d'erreur dans le décodage de protocole

- Chronogramme du bus décodé du protocole.

- Transmission continue de données de protocole vers l'ordinateur hôte pour fournir une grande mémoire tampon.

- Liste des activités du protocole.

- À différentes vitesses, un script d'exercice peut être écrit pour combiner la génération de plusieurs trames de données.

Chronogramme

La chronogramme du JTAG protocole est présenté ci-dessous. Dans le schéma suivant, la broche TDO reste dans la condition d'impédance élevée, sauf pendant un état de contrôleur shift-IR/shift-DR.

Dans les conditions de contrôleur shift-IR et Shift-DR, la broche TDO est mise à jour sur le front décroissant de TCK via Target et échantillonnée sur le front croissant de TCK via Host.

Les broches TDI et TMS sont simplement échantillonnées sur le front croissant de TCK via Target. Mis à jour sur le front décroissant sinon TCK via l'hôte.

Applications

La Applications JTAG inclure les éléments suivants.

- Joint Test Action Group est fréquemment utilisé dans les processeurs pour fournir le droit d'accès à leurs fonctions d'émulation ou de débogage.

- Tous les CPLD et FPGA l'utilisent comme interface pour donner accès à leurs fonctions de programmation.

- Il est utilisé pour les tests de PCB sans accès physique

- Il est utilisé pour les tests de fabrication au niveau de la carte.

Ainsi, il s'agit de un aperçu de JTAG – configuration des broches, travail avec des applications. La norme industrielle JTAG est utilisée pour la vérification de la conception ainsi que pour les tests de PCB après la fabrication. Voici une question pour vous, JTAG signifie ?