Le terme VLSI signifie «Very Large Scale Integration Technology» qui implique la conception de circuits intégrés (IC) en combinant des milliers de transistors logiquement en une seule puce en différents circuits logiques . Ces CI réduisent finalement l'espace de circuit occupé par rapport aux circuits avec des CI conventionnels. La puissance de calcul et l'utilisation de l'espace sont les principaux défis de la conception VLSI. La mise en œuvre de projets VLSI ouvre une carrière stimulante et brillante pour les étudiants comme pour les chercheurs. Certains des nouveaux domaines de tendance de VLSI sont Réseau de portes programmable sur site applications (FPGA), conceptions ASIC et SOC. Une liste de certains des projets VLSI est donnée ci-dessous pour les étudiants qui recherchent sérieusement des projets dans ce domaine. Cet article présente une vue d'ensemble des projets VLSI basés sur FPGA, Xilinx, IEEE, Mini, Matlab, etc. sont répertoriés ci-dessous. Ces projets sont très utiles pour les étudiants en génie, les étudiants en M.tech.

Projets VLSI pour étudiants en génie

Les projets VLSI avec des résumés pour les étudiants en génie électronique sont discutés ci-dessous.

Projets VLSI

1). Transformation d'ondelettes discrètes basée sur le levage 3D

Ce projet aide à fournir des images très précises en utilisant le codage d'une image sans perdre ses données. Pour y parvenir, ce processus implémente un filtre élévateur en fonction de la transformation de l'architecture VLSI en ondelettes discrètes 3D.

2). Conception d'un multiplicateur SFQ avec 4 bits avec efficacité grâce au matériel haute vitesse

Ce projet est principalement utilisé pour implémenter un encodeur de cabine modifié (MBE) avec SFQ 4 bits basé multiplicateur . Ce multiplicateur offre de bonnes performances par rapport à l'encodeur de cabine conventionnel. Ce projet est principalement utilisé dans les applications de délai critique.

3). Processeur de cryptographie utilisé dans les cartes à puce avec une zone efficace

Ce projet est utilisé pour implémenter trois algorithmes de cryptographie pris en charge par des clés privées et publiques utilisées dans carte à puce applications pour fournir une vérification et des données utilisateur extrêmement sécurisées la communication .

4). Multiplicateur haute vitesse ou faible puissance avec méthode de suppression de la puissance parasite

Ce système proposé filtre les faux signaux inutiles des unités arithmétiques pour éviter une transmission de données inutile qui n'influence pas les derniers résultats de calcul. Ce système utilise une méthode SPST pour les multiplicateurs afin d'obtenir une transmission de données à faible puissance et à grande vitesse.

5). Compression et décompression d'un algorithme de données sans perte

Ce projet est principalement implémenté pour une architecture matérielle en 2 étapes en fonction de la fonctionnalité d'algorithme PDLZW (Parallel Dictionary LZW) ainsi que de l'algorithme de type Adaptive Huffman qui est utilisé à la fois pour les applications de compression de données sans perte et de décompression sans perte.

6). L'architecture du turbo-décodeur à faible complexité pour les réseaux WSN écoénergétiques

Le système proposé est utilisé pour réduire la consommation totale d'énergie tout au long de la transmission de données des WSN grâce à l'algorithme de décomposition de LUT-Log-BCJR aux opérations ACS de base (Add Compare Select).

7). Architecture VLSI pour supprimer efficacement le bruit impulsionnel d'une image

Ce système proposé est principalement utilisé pour améliorer visuellement la qualité de l'image pour éviter les risques de corruption par le bruit impulsif pour mettre en œuvre une architecture VLSI efficace à l'aide d'un filtre préservant les bords.

8). L'architecture d'un processeur en mémoire utilisé pour la compression du multimédia

Ce système proposé fournit une architecture de faible complexité pour un processeur en mémoire pour prendre en charge les applications multimédias, à savoir la compression d'image, la vidéo en appliquant d'énormes concepts à instruction unique, plusieurs concepts de données et mot d'instruction.

9). Technique de synchronisation temporelle avec un débit de symboles pour les systèmes OFDM sans fil à faible puissance

Ce système proposé principalement utilisé pour améliorer l'action de l'OFDM sans fil (Orthogonal Frequency Division Multiplexage ) en diminuant la puissance de toute la bande de base à l'aide d'une horloge Générateur avec contrôleur de synchronisation d'échantillonnage dynamique et accordable en phase.

dix). Implémentation de multiplicateur basse consommation et haute vitesse basée sur un accumulateur avec SPST Adder et Verilog

Ce projet est utilisé pour concevoir un MAC (multiplicateur et accumulateur) basse puissance et haute vitesse en acceptant la méthode de suppression de fausse puissance sur un MBE (encodeur de cabine modifié). En utilisant cette conception, la dissipation de puissance de la commutation entière peut être évitée.

11). Conception et mise en œuvre de processeurs de robot en activant l'anti-collision avec la technologie RFID

Le système proposé est principalement utilisé pour mettre en œuvre un robot processeur avec anti-collision pour éviter la collision physique de robots dans l'environnement de multi-robot. Cet algorithme est principalement implémenté en utilisant la technologie VHDL et RFID.

12). Conception d'un circuit logique économe en énergie à l'aide de la méthode adiabatique

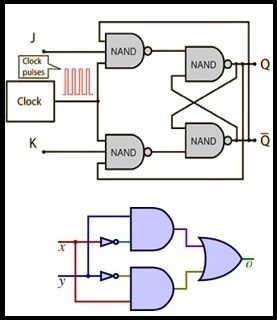

Ce système démontre la conception du circuit logique de manière efficace avec une méthode adiabatique par rapport à une conception CMOS conventionnelle à l'aide de circuits utilisant Portes NAND & NOR . En utilisant la méthode adiabatique, la dissipation de puissance au sein du réseau peut être réduite et recycle l'énergie stockée dans le condensateur de charge.

3). Système de cryptage pour améliorer la vitesse de calcul du système

L'intention principale de ce projet est d'améliorer la sécurité de la transmission des données pour améliorer la vitesse de calcul en implémentant l'algorithme d'AES en utilisant FPGA. Ainsi, cette simulation, ainsi que la conception mathématique, peuvent être effectuées à l'aide du code VHDL.

14). Bloc IP d'AHM ou bus haute performance avancé

Ce projet est principalement utilisé pour concevoir une architecture du Advanced Microcontrôleur Bus (AMB) en utilisant AHBN (Advanced High-Performance Bus). Ce projet peut être conçu avec du code VHDL en implémentant les blocs tels que master & save.

15). Émetteur-récepteur RF multimode basé sur DSM avec un canal multicanal

Ce système est principalement utilisé pour concevoir une architecture d'émetteur et de récepteur multimode et multicanal RF avec un modulateur Delta-Sigma. Ce système proposé utilise un langage VHDL pour implémenter deux architectures.

16). Le concentrateur de Knockout Switch utilisant un mode de transfert asynchrone

En utilisant ce projet, un commutateur knockout basé sur le transfert asynchrone peut être conçu à l'aide d'outils tels que VHS et VHDL. Ce commutateur knock-out peut être utilisé dans les réseaux de paquets de circuits virtuels ainsi que dans les applications du datagramme.

17). Synthèse comportementale des circuits asynchrones

Ce projet est principalement utilisé pour fournir la technique de synthèse comportementale utilisée pour les circuits asynchrones. Les modèles comme les implémentations balsa et asynchrones sont les principaux éléments de la conception.

18). Conception AMBA utilisant un contrôleur de mémoire conforme d'AHB

Ce projet est utilisé pour concevoir un MC (contrôleur de mémoire) en fonction de AMBA (Advanced Microcontroller Bus Architecture) pour le contrôle de la mémoire système en utilisant la mémoire principale comme SRAM et ROM.

19). Implémentation de Carry Tree Adder

Les additionneurs d'arborescence porteuse basés sur la conception VLSI sont appelés les meilleurs additionneurs de performances, contrairement aux additionneurs binaires habituels. Les additionneurs qui sont mis en œuvre par ce projet sont des arbres, des kogge-stone et des kogge-stone clairsemés.

20). Rotation d'angle fixe basée sur la conception CORDIC

Le concept principal de ce système proposé est de faire tourner des vecteurs en utilisant des angles fixes. Ces angles sont nécessaires pour les jeux, la robotique, traitement d'image , etc. En utilisant ce projet, la rotation vectorielle peut être obtenue en utilisant des angles spécifiques par la conception de CORDIC (ordinateur numérique de rotation de coordonnées).

21). Conception de filtre FIR avec arithmétique distribuée de la table de consultation

Ce système proposé améliore principalement Filtre FIR performances en le concevant à l'aide de l'arithmétique distribuée d'une table de consultation en 3 dimensions à la place du multiplicateur. Cette conception peut donc être mise en œuvre à l'aide de logiciels tels que FPGA et Xilinx.

22). Loquets pulsés push-pull avec conditions haute vitesse et faible puissance

Ce projet est utilisé pour exécuter des verrous pulsés écoénergétiques et hautes performances principalement utilisés pour les systèmes VLSI en utilisant une nouvelle topologie. Parce que cette topologie dépend principalement d'une étape finale push-pull pilotée à l'aide de deux voies de division via un générateur d'impulsions conditionnelles.

23). Architecture VLSI du codeur arithmétique dans SPIHT

Ce système proposé améliore le débit de la méthode de codage arithmétique dans la compression d'image de partitionnement en arbres hiérarchiques (SPIHT) avec l'architecture à grande vitesse dépendant de FPGA.

24). Suppression du bruit du signal ECG basé sur FPGA

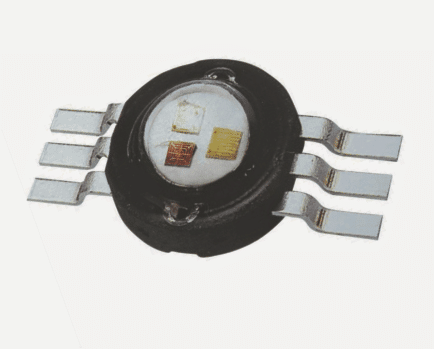

Ce projet est utilisé pour contenir le bruit dans les signaux ECG à travers deux filtres médians avec respectivement 91 et 7 tailles de points d'échantillonnage. Ainsi, ce processus peut être atteint en mettant en œuvre le Conception FPGA basé sur le code VHDL.

25). Processeur de mise à l'échelle d'image haute performance basé sur VLSI à faible coût

Ce projet est utilisé pour implémenter un algorithme pour le processeur de mise à l'échelle d'image basé sur VLSI avec moins de mémoire et des performances élevées. La conception du système proposé contient principalement une combinaison de filtres, de méthodes dynamiques reconfigurables et de partage de matériel pour réduire le coût.

26). Conception et mise en œuvre efficaces de l'architecture de réseau systolique

Le concept principal de ce projet est de concevoir un modèle matériel utilisé pour le multiplicateur de réseau systolique. Ce tableau peut être principalement utilisé pour exécuter une multiplication binaire à l'aide de la plate-forme VHDL. La conception de système proposée peut être mise en œuvre à l'aide du logiciel FPGA et Isim.

27). Conception et synthèse QPSK à l'aide du code VHDL

QPSK est l'une des principales méthodes de modulation. Cette méthode est utilisée dans les applications de la radio par satellite. Cette technique de modulation peut être mise en œuvre à travers des portes logiques réversibles. La conception de la technique QPSK peut être réalisée à l'aide du code VHDL.

28). Conception et mise en œuvre de contrôleurs DDR SDRAM à haute vitesse

Le système proposé est utilisé pour concevoir un contrôleur DDR SDRAM pour transférer les données en rafale en fonction de la vitesse élevée pour synchroniser ces données entre les circuits du système embarqué et la DDR SDRAM. En utilisant le langage VHDL, le code peut être développé.

29). Conception et mise en œuvre de processeurs RISC 32 bits

Le concept principal de ce projet est d'implémenter un 32 bits RISC (ordinateur à jeu d'instructions réduit) à l'aide d'un outil comme XILINK VIRTEX4. Dans ce projet, 16 jeux d'instructions sont conçus partout où chaque instruction peut être exécutée en un seul cycle CLK en utilisant la méthode de pipelining en cinq phases.

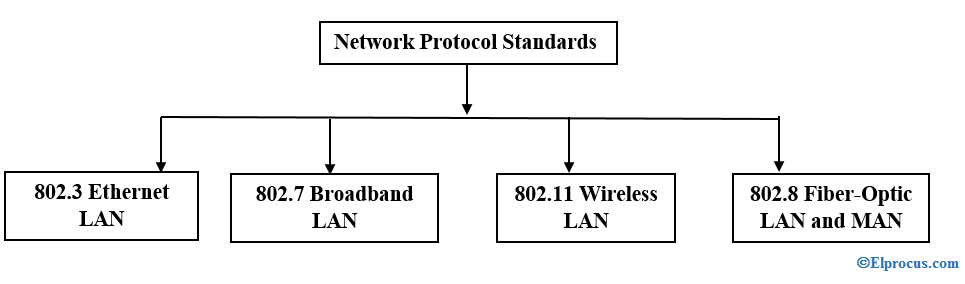

30). Implémentation de pont de bus entre AHB et OCP

Le système proposé est utilisé pour concevoir un pont de bus entre deux protocoles à savoir commun et standard. Les protocoles de communication comme AHB (Advanced High-Performance Bus) et OCP (Open Core Protocol) sont très populaires et sont utilisés dans les applications de SoC (système sur puce) .

Idées de projets VLSI pour les étudiants en génie

La liste des projets VLSI basés sur FPGA, MatLab, IEEE et Mini Projets pour les étudiants en génie est répertoriée ci-dessous.

Projets VLSI pour étudiants M. Tech

La liste des projets VLSI basés sur les étudiants M. Tech comprend les éléments suivants.

- Conception de cellules mémoire I0T basée sur la technologie RHBD et hautement fiable utilisée dans les applications aérospatiales

- Détecteur de phase avec demi-débit à plusieurs niveaux utilisé pour les circuits CLK et de récupération de données

- Comparateur à faible puissance et haute vitesse utilisé pour des applications précises

- Traducteur de niveau de tension Gated avec un multiplexeur intégré haute performance

- Additionneur ternaire basé sur CNTFET avec haute performance

- Conception de comparateur de magnitude à faible puissance

- Conception de la porte logique à seuil avec mode courant pour l'analyse des retards

- Conception de décodeurs de ligne à logique mixte avec faible puissance et hautes performances

- Conception de testabilité de logique de convention de sommeil

- Shifter de niveau de tension pour les applications à double alimentation avec une haute vitesse et une efficacité énergétique

- Conception et analyse de comparateurs à double queue basse puissance et basse tension

- Conception de bascule basée sur le déclenchement par impulsion avec une faible puissance en utilisant une méthode de traversée du signal

- Conception de circuits efficace basée sur des FET reconfigurables à l'exécution

- Conception de comparateur de magnitude à faible puissance

- Analyse du retard des conceptions de portes logiques avec seuil de mode courant

Le Projets VLSI basés sur FPGA pour les étudiants ingénieurs et Mini-projets de conception CMOS VLSI sont énumérés ci-dessous.

- Conception et caractérisation de circuits durcis SEU pour FPGA basés sur SRAM

- Une conception et une application potentielle de LUT hybride CMOS basée sur un Compact Memristor utilisé dans FPGA

- Implémentation basée sur un capteur à ultrasons de FPGA pour la mesure de distance

- Implémentation de FPGA pour Booth Multiplier avec FPGA Spartan6

- Transformation en ondelettes discrète basée sur le levage avec le FPGA Spartan3

- Contrôleur ARM en robotique utilisant FPGA

- UART basé sur FPGA avec multicanal

- Suppression du bruit du signal ECG à l'aide de FPGA

- Implémentation FPGA basée sur UTMI et couche de protocole USB 2.0

- Implémentation du filtre médian avec le FPGA Spartan3

- Implémentation basée sur un algorithme AES de FPGA

- Système d'alerte de sécurité basé sur PIC pour la mise en œuvre de FPGA avec Spartan 3an

- Implémentation FPGA pour concevoir le contrôleur des systèmes de télédétection

- Kit de traitement d'image de FPGA utilisant le filtrage d'image linéaire et morphologique

- Implémentation d'image de fusion médicale basée sur Spartan3 FPGA

La liste de Mini projets VLSI utilisant du code VHDL comprend les éléments suivants.

- Comparateur avec haute vitesse utilisant VLSI

- Un multiplicateur de virgule flottante utilisant VLSI

- Conversion basée sur VLSI de binaire en gris

- Filtre numérique

- CLK Gating basé sur VLSI

- Multiplicateur védique

- CMOS FF utilisant VLSI

- L'architecture du processeur parallèle utilisant VLSI

- Additionneur complet basé sur VLSI

- Conception de DRAM / mémoire à accès aléatoire dynamique basée sur VLSI

- Disposition SRAM basée sur VLSI

- Processeur de signal numérique basé sur VLSI

- Multiplexeur basé sur VLSI

- Conception de l'unité MAC basée sur VLSI

- Différentiateur basé sur VLSI

- FFT ou transformation de Fourier rapide basée sur VLSI

- L'architecture de la transformation cosinus discrète basée sur VLSI

- Conception de multiplicateur 16 bits utilisant VLSI19

- Conception basée sur VLSI du tampon FIFO

- Accélérateur haute vitesse basé sur VLSI

Projets VLSI utilisant MATLAB et Xilinx

La liste des projets VLSI basés sur les projets MATLAB et VLSI utilisant Xilinx comprend les éléments suivants.

- Conception et analyse de modem CDMA avec MATLAB

- Conception de filtres FIR utilisant VHDL sur une analyse basée sur FPGA et MATLAB

- ModelSim & Matlab ou Simulink Simulation d'un système pour l'ingénierie automobile

- Adders basés sur Xilinx comme Ripple Carry & Carry Skip

- Unité arithmétique basée sur la virgule flottante 32 bits

- ALU à virgule flottante

- Processeur RISC basé sur 32 bits

- Capacités de convolution du code orthogonal

- Distributeur automatique basé sur Xilinx et Verilog

- Addeurs de préfixes parallèles basés sur Xilinx avec 256 bits

- Protocole d'authentification mutuelle à l'aide de Xilinx

- Structure d'accès avec un cycle unique pour le test logique à l'aide de Xilinx

- UTMI et protocole USB2.0 basé sur Xilinx

- Configuration de la compression et de la décompression des données à l'aide de Xilinx FPGA

- FPGA basés sur Xilinx 4000 basés sur les séries BIST et Spartan

- Filtre IIR basé sur MATLAB et VLSI

- Filtre FIR avec MATLAB

Projets IEEE

Le liste des projets IEEE VLSI est listé ci-dessous.

- Système domotique sans fil basé sur VLSI utilisant Bluetooth

- Suppression du bruit impulsionnel dans l'image à l'aide d'une architecture efficace de VLSI

- L'architecture d'un processeur en mémoire pour la compression multimédia

- Surveillance du système de température à l'aide du cloud et de l'IoT

- Implémentation du système OFDM avec IFFT et FFT

- Conception et mise en œuvre de code Hamming avec Verilog

- Reconnaissance d'empreintes digitales basée sur VHDL à l'aide du filtre Gabor

- Remappage des fonctions arithmétiques avec ROM en fonction des approches d'approximation

- Analyse des performances à haut rendement et à faible densité du décodeur de code de contrôle de parité dans les applications à faible puissance

- Architectures FFT avec feedforward de Pipelined Radix-2k

- Conception de bascules pour les applications VLSI utilisant la technologie CMOS à haute performance

- Conception de filtre FIR avec table de consultation par arithmétique distribuée

- Processeur de mise à l'échelle d'image amélioré basé sur VLSI

- Implémentation ASIC et conception d'un encodeur et décodeur Turbo avancé avec 3GPP LTE

- Loquets pulsés push-pull à faible puissance et haute vitesse conditionnels

- Analyse améliorée dans les tests d'analyse à faible consommation

- Architecture VLSI du codeur arithmétique pour SPIHT

- Implémentation de VHDL pour UART

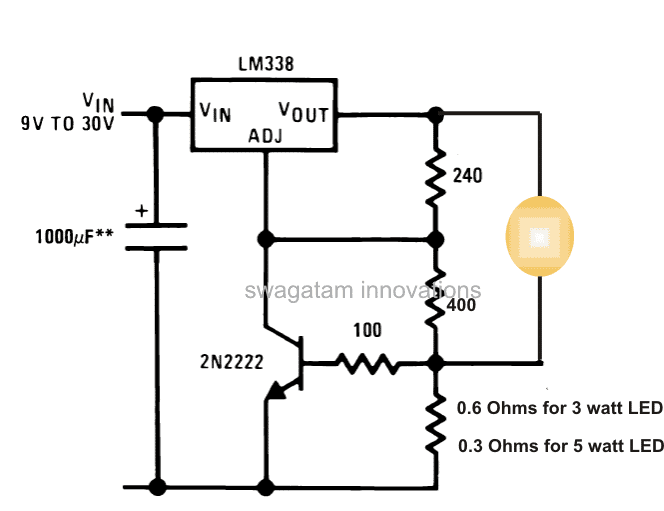

- Régulateur de tension basé sur VLSI avec faible chute de sortie

- Conception Flash ADC avec schéma de comparaison amélioré

- Conception de multiplicateur de faible puissance avec style logique à retard constant composé

- Comparateur double queue avec haute performance et faible puissance

- Système de stockage Flash avec hautes performances en fonction du tampon d'écriture et de la mémoire virtuelle

- Low Power FF basé sur l'approche Sleepy Stack

- Optimisation de la puissance LFSR pour BIST basse consommation implémentée en HDL

- Conception et mise en œuvre de distributeurs automatiques avec Verilog HDL

- Conception d'accumulateur basée sur la génération d'un modèle à 3 poids avec LP-LSFR

- Décodeur Reed-Solomon avec haute vitesse et faible complexité

- Technique de conception plus rapide du multiplicateur Dadda

- Récepteur de radio FM basé sur la démodulation numérique

- Génération de motif de test avec des schémas BIST

- Implémentation de l'architecture VLSI avec pipeline à grande vitesse

- Conception de protocole OCP de bus sur puce utilisant les fonctionnalités de bus

- Détecteur de fréquence de phase et conception de pompe de charge utilisée pour la boucle à verrouillage de phase haute fréquence

- Conception de la mémoire cache et du contrôleur de cache avec VHDL

- Implémentation basée sur ASTRAN de compresseurs additionnels 3-2 et 4-2 basse consommation

- Système de facturation d'électricité prépayée utilisant une conception sur puce

- Implémentation de chevauchement à l'aide de la cellule logique et de son analyse de puissance

- Avancez Look Ahead Adder avec différentes analyses des performances de bits à l'aide de VHDL

- Conception de couche de liaison de données avec Wi-Fi MAC Protocoles

- Implémentation de FPGA pour le protocole d'authentification mutuelle avec arithmétique modulaire

- Génération de signaux PWM à l'aide de FPGA et d'un cycle de service variable

Projets en temps réel

La liste de Projets en temps réel VLSI comprennent principalement des mini-projets VLSI utilisant du code VHDL et des projets logiciels VLSI pour les étudiants en ingénierie de la CEE.

- Intégration pragmatique de SRAM Row Cache dans une architecture DRAM 3D hétérogène à l'aide de TSV

- Technique d'autotest intégrée pour le diagnostic des défauts de retard dans les réseaux de portes programmables en grappe

- Conception ASIC d'un multiplicateur complexe

- Une implémentation VLSI à faible coût pour une élimination efficace du bruit impulsionnel

- Basé sur FPGA Vecteur spatial PWM CI de contrôle pour entraînement de moteur à induction triphasé

- Implémentation VLSI du corrélateur automatique et de l'algorithme CORDIC pour le WLAN basé sur OFDM

- Extraction automatique de la route à l'aide d'images satellites haute résolution

- Conception VHDL pour la segmentation d'image à l'aide du filtre Gabor pour la détection des maladies

- Une architecture de turbo-décodeur à faible complexité pour les réseaux de capteurs sans fil à faible consommation d'énergie

- Amélioration des capacités de convolution du code orthogonal à l'aide de l'implémentation FPGA

- Conception et mise en œuvre de l'ALU à virgule flottante

- Conception CORDIC pour angle de rotation fixe

- Codes de produit Reed-Solomon pour la mise en œuvre du contrôleur Flash NAND sur une puce FPGA

- Amélioration statistique du rendement d'accès en lecture SRAM à l'aide de circuits de capacité négative

- Gestion de l'alimentation des interfaces réseau MIMO sur les systèmes mobiles

- Conception d'une norme de cryptage des données pour le cryptage des données

- Additionneur de sélection de transport à faible consommation d'énergie et efficace

- Synthèse et implémentation d'UART à l'aide de codes VHDL

- Architectures améliorées pour une unité d'addition-soustraction à virgule flottante fusionnée

- Un émetteur tout numérique 1 bit basé sur FPGA utilisant une modulation Delta-Sigma avec sortie RF pour SDR

- Optimisation de l'utilisation de la recherche en chaîne dans le décodeur BCH pour une transmission à taux d'erreur élevé

- Conception numérique de l'émetteur DS-CDMA utilisant Verilog HDL et FPGA

- Conception et mise en œuvre d'une architecture de réseau systolique efficace

- Un algorithme d'apprentissage de la dynamique du robot basé sur VLSI

- Une conception d'unité fonctionnelle multimédia polyvalente utilisant la technique de suppression de la puissance parasite

- Conception du pont de bus entre AHB et OCP

- Synthèse comportementale des circuits asynchrones

- Optimisation de la vitesse d'un décodeur Viterbi modifié basé sur FPGA

- Implémentation de l'interface I2C

- Un multiplicateur haute vitesse / faible puissance utilisant une technique avancée de suppression de la puissance parasite

- Serrage de la tension d'alimentation virtuelle des circuits à commande électrique pour la réduction active des fuites et la fiabilité de l'oxyde de porte

- Channelizer à efficacité énergétique basé sur FPGA pour la radio définie par logiciel

- Architecture VLSI et prototypage FPGA d'un appareil photo numérique pour la sécurité d'image et l'authentification

- Amélioration du fonctionnement du robot d'intérieur

- Conception et mise en œuvre d'un réseau de permutation sur puce pour un système sur puce multiprocesseur

- Une méthode de synchronisation de synchronisation à débit de symboles pour les systèmes OFDM sans fil à faible puissance

- Contrôleur DMA (accès direct à la mémoire) à l'aide de VHDL / VLSI

- FFT reconfigurable à l'aide de l'architecture basée sur CORDIC pour les récepteurs MIMI-OFDM

- Technique de suppression de la puissance parasite pour les applications multimédia / DSP

- L'efficacité des codes BCH dans le filigrane d'images numériques

- Contrôleur SD-RAM à double débit de données

- Implémentation du filtre Gabor pour la reconnaissance d'empreintes digitales à l'aide de Verilog HDL

- Conception d'une échelle nanométrique pratique redondante via une bibliothèque de cellules standard Aware pour une redondance améliorée via 1 taux d'insertion

- Un algorithme de compression et de décompression de données sans perte et son architecture matérielle

- Un cadre pour la correction des erreurs logicielles multi-bits

- Compression efficace des données de test basée sur Viterbi

- Implémentation de blocs FFT / IFFT pour l'OFDM

- Compression d'image basée sur des ondelettes par codage progressif VLSI

- Implémentation VLSI d'un multiplicateur entièrement pipeliné sans architecture DCT / IDCT 2D pour Jpeg

- Émulation de défaut basée sur FPGA des circuits séquentiels synchrones

Il s'agit donc de la liste des projets VLSI pour l'ingénierie, des étudiants en M.Tech qui sont utiles pour choisir le sujet de leur projet de dernière année. Après avoir passé votre temps précieux à parcourir cette liste, nous pensons que vous avez une assez bonne idée de sélectionner le sujet de projet de votre choix dans la liste des projets VLSI, et espérons que vous avez suffisamment de confiance pour aborder n'importe quel sujet du liste. Pour plus de détails et une aide sur ces projets, vous pouvez nous écrire dans la section commentaires ci-dessous. Voici une question pour vous, qu'est-ce que VHDL?

Crédit photo

- Projets VLSI par ensemble-tech