Le processeur MicroBlaze a été développé en 2002 pour intégrer plusieurs fonctionnalités complexes afin de répondre à la demande nouvelle et croissante du marché. Ainsi, le processeur MicroBlaze est un élément essentiel du portefeuille bas de gamme de Xilinx pour permettre un développement plus rapide du système qui contient Artix®-7 FPGA , Spartan®-6, Zynq®-7000 AP SoC. Ce processeur est extrêmement configurable, il peut donc être utilisé comme processeur intégré ou microcontrôleur dans les FPGA et également utilisé comme coprocesseur dans les SoC Zynq-7000 AP basés sur ARM Cortex-A9. Cet article donne de brèves informations sur Processeur MicroBlaze – l'architecture et l'utilisation des applications.

Qu'est-ce que le processeur Microblaze ?

Le microprocesseur logiciel conçu principalement pour les FPGA de Xilinx est connu sous le nom de processeur MicroBlaze. Ce processeur est simplement implémenté dans la mémoire à usage général et la structure logique des FPGA de Xilinx. Ce processeur est similaire à l'architecture DLX basée sur RISC et dispose d'un système d'interconnexion flexible afin de prendre en charge différentes applications embarquées. Le bus d'E/S principal et l'interconnexion AXI du MicroBlaze est un bus de transaction mappé en mémoire avec une fonction maître-esclave.

MicroBlaze utilise un bus LMB dédié pour accéder à la mémoire locale et fournit un stockage rapide sur puce. De nombreuses parties de ce processeur peuvent être configurées par l'utilisateur, comme la taille du cache, la profondeur de l'unité de gestion de la mémoire du pipeline, les périphériques intégrés et les interfaces de bus.

Caractéristiques de Microblaze

La caractéristiques de Microblaz e inclure les éléments suivants. Il dispose de 32 registres à usage général.

- Il dispose de mots d'instruction de 32 bits comprenant 2 modes d'adressage et 3 opérandes.

- Le bus d'adresse est de 32 bits.

- Il a un pipeline à 3 étages ou un pipeline à 5 étages.

- Une unité de bloc ALU avec un levier de vitesses.

- L'architecture Harvard comprend un bus de données et d'adresses 32 bits.

- Interface de données et instruction LMB ou bus de mémoire locale.

- Interfaces de flux AX14 et AX14.

- Unité à virgule flottante et unité de gestion de la mémoire.

- Il prend en charge le verrouillage.

- Interface de débogage et de suivi.

Architecture microbienne

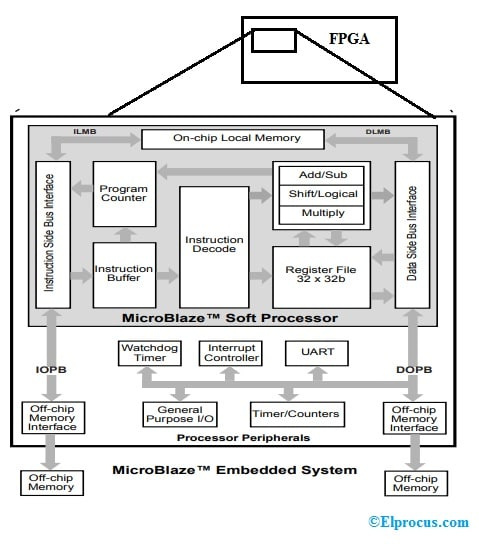

Le schéma fonctionnel du processeur MicroBlaze est illustré ci-dessous. Ce processeur MicroBlaze est extrêmement personnalisable et prend en charge plus de 70 options de conception. Cette architecture présente des fonctionnalités matérielles permanentes ainsi que des options configurables telles que le cache d'instructions ou de données, l'unité de gestion de la mémoire, l'unité à virgule flottante, etc.

Un système embarqué assemblé autour d'un processeur MicroBlaze comprend principalement le cœur de processeur MicroBlaze Soft, la mémoire locale sur puce, les interconnexions de bus standard et les périphériques OPB (bus périphérique sur puce). Un système de processeur MicroBlaze va principalement d'un cœur de processeur par une mémoire locale à un grand système comprenant plusieurs MicroBlaze processeurs , mémoire externe et de nombreux périphériques OPB.

Noyau de processeur souple

Le cœur du processeur logiciel de MicroBlaze est au cœur du système embarqué MicroBlaze. Il s'agit d'un processeur RISC 32 bits très rapide et efficace qui présente les caractéristiques suivantes.

- Le jeu d'instructions est orthogonal.

- Bus de données et d'instructions séparés.

- Registres à usage général 32 bits.

- Il dispose d'un levier de vitesses complet 32 bits en option.

- Interfaces intégrées pour OCM rapide ou mémoire sur puce et OPB (On-chip Peripheral Bus) standard de l'industrie d'IBM.

Les implémentations dans Virtex-II et les appareils ultérieurs prennent en charge la multiplication du matériel.

Mémoire locale sur puce

La mémoire synchrone est une mémoire locale qui est principalement utilisée pour autoriser la RAM bloc sur puce.

Interconnexions de bus standard

Les interfaces de bus côté instructions et données comprennent une interface vers la mémoire locale appelée LMB (Local Memory Bus) et une interface vers le bus périphérique sur puce d'IBM. Nous pouvons donc concevoir des systèmes strictement conformes à l'architecture de Harvard, sinon, pour partager les ressources, nous pouvons utiliser un seul OPB en combinaison via un arbitre de bus.

Le bus de mémoire local assure une entrée à cycle unique pour la RAM de bloc sur puce. Il s'agit d'un protocole de bus très efficace, simple et à maître unique, parfait pour interfacer une mémoire locale rapide. L'OPB ou On-chip Peripheral Bus est un bus multi-maître large de 32 bits qui est parfait pour unir les périphériques et la mémoire extérieure au cœur du processeur MicroBlaze.

Périphériques de bus périphériques sur puce

Le système matériel MicroBlaze est complété par des périphériques OPB pour fournir différentes fonctions comme Watchdog Timer ou Timebase, General Purpose Timer ou Counters, IC (Interrupt Controller), différents contrôleurs comme SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, E/S à usage général, UART 16450/550 et Ethernet 10/100 MAC. De plus, nous pouvons également ajouter et définir des périphériques principalement pour des fonctions personnalisées, sinon une interface vers une conception qui existe dans le FPGA.

Ensemble d'instructions Microblaze

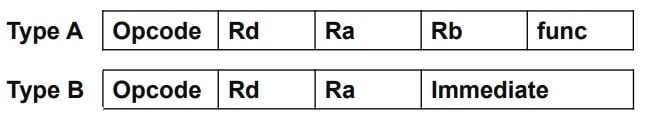

Les jeux d'instructions Microblaze sont l'arithmétique, la logique, la branche, le chargement/stockage et autres. La taille de toutes les instructions est fixe. Au plus 3 registres peuvent être donnés comme opérandes. Microblaze comprend deux formats d'instructions Type A et Type B qui sont présentés ci-dessous.

Le format d'instruction de type A est principalement utilisé pour les instructions registre-registre. Il inclut donc l'opcode, une destination unique et deux registres source. Le format d'instruction de type B est principalement utilisé pour les instructions immédiates au registre qui incluent les registres d'opcode, de destination unique et de source unique. & une source de valeur immédiate de 16 bits.

Dans les deux formats d'instruction ci-dessus, l'opcode est un code d'opération, Rd est un registre de destination qui est codé avec 5 bits, Ra et Rb sont des registres source où chacun est codé avec 5 bits et Immediate est une valeur 16 bits.

Instructions arithmétiques

Les instructions arithmétiques de type A et de type B sont données ci-dessous.

Type A

|

AJOUTER Rd, Ra, Rb ajouter |

Rd = Ra+Rb, Carry flag affecté |

|

AJOUTER K Rd, Ra, Rb Ajouter et conserver |

Rd = Ra+Rb, Carry flag non affecté |

| RSUB Rd, Ra, Rb Soustraction inverse |

Rd = R-Rb, Carry flag non affecté |

Tapez B

|

AJOUTER I Rd, Ra, Imm ajouter immédiatement |

Rd = Ra+signExtend32 (Imm) |

|

AJOUTER IK Rd, Ra, Imm ajouter immédiatement et garder emporter |

Rd = Ra+ signExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm soustraction inverse avec effet immédiat |

Rd = Ra+ signExtend32 (Imm) -Ra |

| Chemin SRA, Ra décalage arithmétique vers la droite |

Rd = (Ra>>1) |

Instructions logiques

Les instructions logiques de type A et de type B sont données ci-dessous.

Type A

|

OU Rd, Ra, Rb Logique ou |

Rd = Ra| Rb |

|

ET Rd,Ra,Rb Ajout logique |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb xor logoique |

Rd = Rb ^ Rb |

| Chemin ANDN, Ra, Rb Logique et pas |

Rd = Ra & (Rb) |

Tapez B

|

ORI Rd, Ra, Imm OU logique avec immédiat |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm ET logique avec immédiat |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logoical XOR avec immédiat |

Rd = Ra ^ signExtend32 (Imm) |

| ANDNI Rd, Ra, Imm ET NON logique avec immédiat |

Rd = Ra & (signExtend32 (Imm)) |

Instructions de la succursale - Inconditionnel

Modifier le registre du compteur de programme

| BRID Imm branche immédiate avec délai immédiat |

PC = PC+ signExtend32 (Imm) autoriser l'exécution de l'emplacement de retard |

| Chemin BRLID, Imm branche et lien immédiat avec délai immédiat (appel de fonction) |

Rd = PC PC = PC+& signExtend32 (Imm) autoriser l'exécution de l'emplacement de retard |

| RTSD Ra, Imm retour de sous-programme |

PC = Ra + signExtend32 (Imm) autoriser l'exécution de l'emplacement de retard |

| RTID Ra, Imm retour d'interruption |

PC = Ra + signExtend32 (Imm) autoriser l'exécution de l'emplacement de retard définir l'autorisation d'interruption dans MSR |

Instructions de la succursale - Inconditionnel1

Modifier le registre du compteur de programme lorsqu'une condition est satisfaite

| BEQI Ra, Imm branche si égale |

PC = PC+ signExtend32 (Imm) Si Ra = = 0 |

| MASH Ra, Imm branche sinon égale |

Rd = PC PC = PC+& signExtend32 (Imm) Si Ra! = 0 |

Instructions de la succursale - Inconditionnel2

Modifier le registre du compteur de programme lorsqu'une condition est satisfaite

| BLTI Ra, Imm branche si inférieur à |

PC = PC+ signExtend32 (Imm) Si Ra < 0 |

| BLEI Ra, Imm branche si inférieur égal à |

Rd = PC PC = PC+& signExtend32 (Imm) Si Ra!< = 0 |

| BGTI Ra, Imm branche si supérieur à |

PC = PC+ signExtend32 (Imm) Si Ra!> 0 |

| BGEI Ra, Imm branche si supérieur égal à |

PC = PC+signExtend32 (Imm) Si Ra!>= 0 |

Instructions de chargement/stockage -Type A

| LW Rd, Ra, Rb Mot de charge |

Adresse = Ra+Rb Rd = *Adresse |

| SO Rd, Ra, Rb Stocker le mot |

Adresse – Ra+Rb *Adresse = Chemin |

Tapez B

| LWI Rd, Ra, Imn Charger le mot immédiatement |

Adresse = Ra + signExtend32 (Imm) Rd = *Adresse |

| SW Rd, Ra, Imm Stocker le mot immédiatement |

Adresse = Ra + signExtend32 (Imm) *Adresse = Chemin |

Autres consignes

| IMM, Imm immédiat |

Étendez l'Imm d'une instruction de type B précédente à 32 bits. |

| Chemin MFS, Sa Déplacer du registre à usage spécial |

Rd = Sa Sa- registre à usage spécial, opérande source

|

| MTS Sd, Ra Passer au registre à usage spécial |

Sd = Ra Sd - registre à usage spécial, opérande de destination |

Registres

L'architecture du processeur MicroBlaze est complètement orthogonale et comprend des registres à usage général 32 bits et des registres à usage spécial 32 bits comme le compteur de programme et le registre d'état de la machine.

Architecture de pipeline

MicroBlaze utilise une architecture de pipeline en 3 étapes comprenant les étapes de récupération, de décodage et d'achèvement. Automatiquement, le transfert de données, les branches et le décrochage du pipeline sont déterminés au sein du matériel.

Charger ou stocker l'architecture

MicroBlaze prend en charge la mémoire en trois tailles de données 8 bits (octet), 16 bits (demi-mot) et 32 bits (mot). Ainsi, les accès mémoire sont toujours alignés sur la taille des données. Il s'agit d'un processeur Big-Endian qui utilise l'adresse de l'adresse Big-Endian ainsi que les conventions d'étiquetage une fois qu'il accède à la mémoire.

Interruptions

Une fois qu'une interruption a lieu, ce processeur mettra fin à l'exécution actuelle pour gérer la demande d'interruption en se ramifiant pour interrompre l'adresse vectorielle et stocker l'adresse d'instruction qui doit être exécutée. Ce processeur arrêtera les futures interruptions en effaçant l'indicateur IE (Interrupt Enable) dans le MSR (Machine Status Register).

Comment fonctionne Microblaze ?

Le processeur MicroBlaze prend en charge une largeur de bus de 32 bits et ce cœur de processeur est un moteur basé sur RISC qui comprend un fichier de registre basé sur une RAM LUT 32 bits via des instructions séparées pour l'accès à la mémoire et aux données.

Ce processeur prend simplement en charge à la fois la BlockRAM sur puce et la mémoire externe. Similaire à l' IBM PowerPC ; tous les périphériques utilisent le même bus CoreConnect OPB donc ; les périphériques du processeur sont bien assortis avec PowerPC sur Virtex-II Pro.

Le processeur MicroBlaze offre une flexibilité totale pour choisir la combinaison de fonctionnalités de mémoire, de périphériques et d'interface qui vous fournira le système précis dont vous avez besoin sur un seul FPGA à moindre coût.

Différence N/B Microblaze Vs Risc-V

La différence entre MicroBlaze et RISC v inclure les éléments suivants.

|

Microblaze |

Risc-V |

| Il s'agit d'un noyau de microprocesseur souple principalement conçu pour les FPGA Xilinx.

|

RISC-V est une architecture de jeu d'instructions ancrée dans les principes RISC.

|

| Il utilise l'architecture Harvard RISC. | Il utilise l'architecture du jeu d'instructions. |

| Sa licence est propriétaire (Xilinx) | Sa licence est open source. |

| La profondeur du pipeline est de 3 ou 5. | La profondeur du pipeline est de 5. |

| Ses performances sont de 280 DMIP. | Ses performances sont de 250 DMIP. |

| Sa vitesse est de 235 MHz. | Sa vitesse est de 250 MHz. |

| Il a 1027 LUT. | Il a 4125 LUT. |

| La mise en œuvre de la technologie utilisée est Xilinx FPGA. | L'implémentation de la technologie utilisée est FPGA/ASIC. |

Avantages de Microblaze

La avantages de MicroBlaze inclure les éléments suivants.

- C'est économique.

- Il est hautement configurable.

- Ses performances sont élevées par rapport à ARM.

- Il est pris en charge par un kit de développement intégré.

- C'est un doux microprocesseur cœur.

- Pour vous aider à organiser rapidement votre application, ce processeur comprend trois configurations fixes qui sont liées aux classes de processeur bien connues microcontrôleur, temps réel et processeur d'application.

Applications Microblaze

La applications de MicroBlaze inclure les éléments suivants.

- Ce processeur répond à de nombreuses exigences d'applications différentes telles que l'industrie, l'automobile, la médecine et la consommation, etc.

- Les applications de MicroBlaze vont des simples machines d'état basées sur des logiciels aux contrôleurs complexes utilisés dans les applications embarquées ou les appareils basés sur Internet.

- Il est optimisé pour les applications embarquées telles que le contrôle industriel, la bureautique et l'automobile.

- Le MicroBlaze est capable de communiquer avec un grand nombre de périphériques pour s'adapter aux applications à moyenne échelle.

- La nature douce de ce processeur le rend personnalisable pour différentes applications où les concepteurs peuvent échanger des fonctionnalités pour la taille afin d'atteindre les objectifs de prix et de performances pour les applications médicales, automobiles, industrielles et de sécurité.

Ainsi, il s'agit de un aperçu du Microblaze processeur. Il s'agit d'un cœur de processeur logiciel RISC programmable 32 bits complet. Ce processeur répond à différentes exigences dans différents domaines tels que les marchés des infrastructures grand public, médicaux, industriels, automobiles et de communication. Il est extrêmement configurable, donc utilisé comme processeur ou microcontrôleur intégré dans les FPGA, sinon comme un coprocesseur pour l'ARM. Voici une question pour vous, qu'est-ce que le FPGA?