L'unité de contrôle est le composant principal d'une unité centrale de traitement (CPU) dans les ordinateurs qui peut diriger les opérations pendant l'exécution d'un programme en le processeur /l'ordinateur. La fonction principale de l'unité de contrôle est de récupérer et d'exécuter des instructions dans la mémoire d'un ordinateur. Il reçoit les instructions / informations d'entrée de l'utilisateur et les convertit en signaux de commande , qui sont ensuite transmises à la CPU pour une exécution ultérieure. Il fait partie de l'architecture Von Neumann développée par John Neumann. Il est chargé de fournir les signaux de synchronisation, les signaux de commande et dirige l'exécution d'un programme par la CPU. Il est inclus en tant que partie interne du processeur dans les ordinateurs modernes. Cet article décrit des informations complètes sur l'unité de contrôle.

Qu'est-ce que l'unité de contrôle?

Le composant qui reçoit le signal d'entrée / l'information / l'instruction de l'utilisateur et se convertit en signaux de commande pour l'exécution dans la CPU. Il contrôle et dirige la mémoire principale, l'unité arithmétique et logique (ALU), les périphériques d'entrée et de sortie, et est également responsable des instructions qui sont envoyées au processeur d'un ordinateur. Il récupère les instructions du mémoire principale d'un processeur et envoyé au registre d'instructions du processeur, qui contient le contenu du registre.

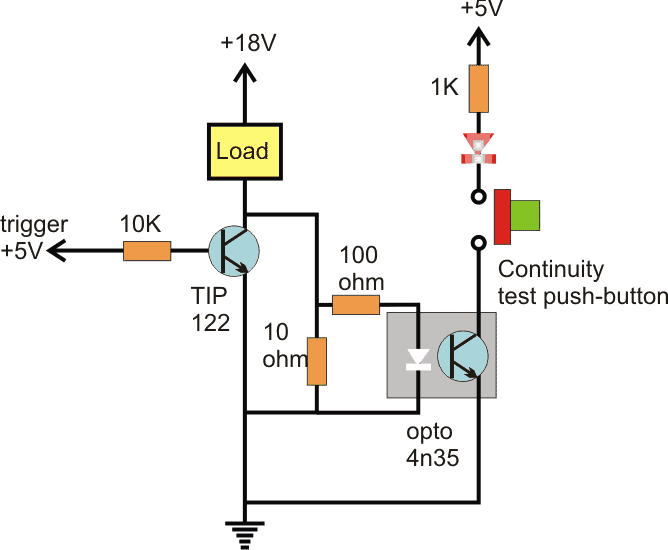

Schéma fonctionnel de l'unité de contrôle

L'unité de contrôle convertit l'entrée en signaux de contrôle puis envoyée au processeur et dirige l'exécution d'un programme. Les opérations à effectuer sont dirigées par le processeur sur l'ordinateur. Unité centrale de traitement (CPU) et Unité de traitement graphique (GPU) nécessitent une unité de contrôle comme partie interne. Le schéma de principe de l'unité de commande est illustré ci-dessus.

Composants d'une unité de contrôle

Les composants de cet appareil sont des instructions registres , des signaux de commande dans la CPU, des signaux de commande vers / depuis le bus, le bus de commande, des drapeaux d'entrée et des signaux d'horloge.

Les composants de l'unité de commande câblée sont le registre d'instructions (contient le code d'opération et le champ d'adresse), l'unité de temporisation, l'état de commande Générateur , matrice de génération de signal de commande et décodeur d'instructions.

Les composants de l'unité de commande programmée Micro sont le générateur d'adresses suivant, un registre d'adresse de commande, une mémoire de commande et un registre de données de commande.

Les fonctions

Le fonctions de l'unité de contrôle inclure les éléments suivants.

- Il dirige le flux de la séquence de données entre le processeur et les autres appareils.

- Il peut interpréter les instructions et contrôler le flux de données dans le processeur.

- Il génère la séquence de signaux de commande à partir des instructions reçues ou des commandes du registre d'instructions.

- Il a la responsabilité de contrôler les unités d'exécution telles que l'ALU, les tampons de données et les registres dans la CPU d'un ordinateur.

- Il a la capacité de récupérer, décoder, gérer l'exécution et stocker les résultats.

- Il ne peut pas traiter et stocker les données

- Pour transférer les données, il communique avec les périphériques d'entrée et de sortie et contrôle toutes les unités de l'ordinateur.

Conception de l'unité de contrôle

La conception de ceci peut être faite en utilisant deux types d'unité de commande qui comprennent les éléments suivants.

- Basé sur le câblage

- Basé sur microprogrammé (un niveau et deux niveaux)

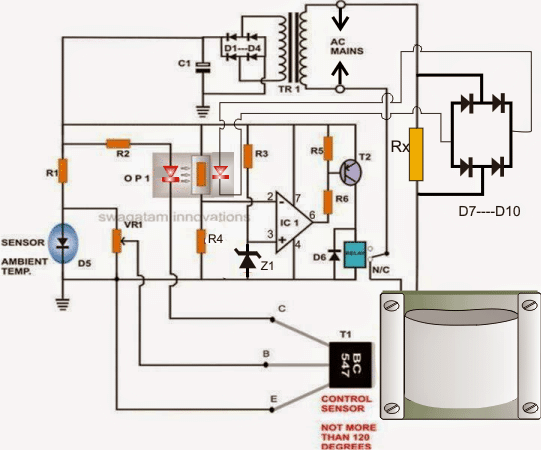

Unité de contrôle câblée

La conception de base d'une unité de commande câblée est illustrée ci-dessus. Dans ce type, les signaux de commande sont générés par un matériel spécial circuit logique sans aucun changement dans la structure du circuit. En cela, le signal généré ne peut pas être modifié pour être exécuté dans le processeur.

Les données de base d'un opcode (le code d'opération d'une instruction est envoyé au décodeur d'instructions pour décodage. L'instruction décodeur est l'ensemble des décodeurs pour décoder différents types de données dans l'opcode. Il en résulte des signaux de sortie qui contiennent des valeurs de signaux actifs qui sont données en entrée du générateur de matrice pour générer des signaux de commande pour l'exécution d'un programme par le processeur de l'ordinateur.

Unité de contrôle câblée

Le générateur de matrice fournit les états de l'unité de commande et les signaux sortant du processeur (signaux d'interruption). Matrix est construit comme le matrice logique programmable . Les signaux de commande générés par le générateur de matrice sont donnés en entrée de la matrice de générateur suivante et se combinent avec les signaux de synchronisation de l'unité de synchronisation qui contient des motifs rectangulaires.

Pour récupérer une nouvelle instruction, l'unité de contrôle se transforme en une étape initiale pour l'exécution d'une nouvelle instruction. L'unité de commande reste à l'étage initial ou au premier étage tant que les signaux de synchronisation, les signaux d'entrée et les états d'instruction d'un ordinateur restent inchangés. Le changement d'état de l'unité de commande peut être augmenté s'il y a un changement dans l'un des signaux générés.

Lorsqu'un signal externe ou une interruption se produit, l'unité de commande passe à l'état suivant et exécute le traitement du signal d'interruption. Les drapeaux et états sont utilisés pour sélectionner les états souhaités pour effectuer le cycle d'exécution de l'instruction.

Dans le dernier état, l'unité de contrôle récupère l'instruction suivante et envoie la sortie au compteur de programme, puis au registre d'adresse mémoire, au registre tampon, puis au registre d'instructions pour lire l'instruction. Enfin, si la dernière instruction (qui est récupérée par l'unité de contrôle) est l'instruction de fin, alors elle passe à l'état de fonctionnement du processeur et attend que l'utilisateur dirige le programme suivant.

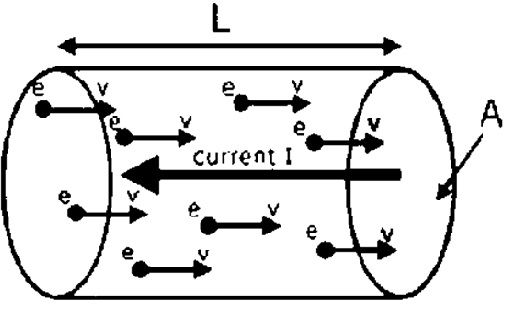

Unité de contrôle micro programmée

Dans ce type, la mémoire de contrôle est utilisée pour stocker les signaux de contrôle qui sont codés lors de l'exécution d'un programme. Le signal de commande n'est pas généré immédiatement et décodé car le microprogramme stocke le champ d'adresse dans la mémoire de commande. L'ensemble du processus est un seul niveau.

Les micro-opérations sont effectuées pour l'exécution de micro-instructions dans le programme. Le schéma fonctionnel de l'unité de commande programmée Micro est illustré ci-dessus. A partir du schéma, l'adresse de la micro-instruction est obtenue à partir du registre d'adresse de la mémoire de contrôle. Toutes les informations de l'unité de contrôle sont stockées en permanence dans la mémoire de contrôle appelée ROM.

Unité de contrôle microprogrammée

La micro-instruction de la mémoire de contrôle est conservée par le registre de contrôle. Étant donné que la micro-instruction se présente sous la forme d'un mot de contrôle (contient des valeurs de contrôle binaires) qui nécessite une ou plusieurs micro-opérations à effectuer pour le traitement des données.

Lors de l'exécution des micro-instructions, le générateur d'adresses suivant a calculé l'adresse suivante de la micro-instruction puis l'envoie au registre d'adresse de contrôle pour lire la micro-instruction suivante.

La séquence de micro-opérations d'un micro-programme est effectuée par le générateur d'adresse suivant et agit comme un séquenceur de microprogramme pour obtenir l'adresse de séquence, c'est-à-dire lue à partir de la mémoire de commande.

Code Verilog pour l'unité de contrôle

Le code Verilog pour l'unité de contrôle est indiqué ci-dessous.

`inclure' prj_definition.v '

module CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, CLUL_WRITE, RF_DATA_R2)

// Signaux de sortie

// Sorties pour le fichier de registre

sortie [`DATA_INDEX_LIMIT: 0] RF_DATA_W

sortie [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

sortie RF_READ, RF_WRITE

// Sorties pour ALU

sortie [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

sortie [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Sorties pour la mémoire

sortie [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

sortie MEM_READ, MEM_WRITE

// Signaux d'entrée

entrée [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

entrée ZERO, CLK, RST

// Signal d'entrée

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Réseaux d'état

fil [2: 0] proc_state

// contient la valeur du compteur de programme, stocke l'instruction courante, registre du pointeur de pile

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

état reg [1: 0], état suivant

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

toujours @ (posedge CLK)

commencer

si (RST)

Etat<= RST

autre

Etat<= next_state

finir

toujours @ (état)

commencer

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

cas (état)

`PROC_FETCH: commencer

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

finir

`PROC_DECODE: commencer

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

finir

`PROC_EXE: commencer

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

finir

`PROC_MEM: commencer

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

finir

`PROC_WB: commencer

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

finir

endcase

finir

module d'extrémité

module PROC_SM (STATE, CLK, RST)

// liste des entrées

entrée CLK, RST

// liste des sorties

sortie [2: 0] STATE

// liste d'entrée

entrée CLK, RST

// liste de sortie

état de sortie

reg [2: 0] STATE

état reg [1: 0]

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`définir PROC_FETCH 3’h0

`définir PROC_DECODE 3’h1

`définir PROC_EXE 3’h2

`définir PROC_MEM 3’h3

`définir PROC_WB 3’h4

// initiation d'état

initiale

commencer

état = 2’bxx

next_state = `PROC_FETCH

finir

// réinitialiser la gestion du signal

toujours @ (posedge RST)

commencer

état = `PROC_FETCH

next_state = `PROC_FETCH

finir

toujours @ (posedge CLK)

commencer

état = état_suivant

finir

toujours @ (état)

commencer

si (état === `PROC_FETCH)

commencer

next_state = `PROC_DECODE

print_instruction (INST_REG)

finir

if (état === `PROC_DECODE)

commencer

next_state = `PROC_EXE

finir

si (état === `PROC_EXE)

commencer

next_state = `PROC_MEM

print_instruction (SP_REF)

finir

si (état === `PROC_MEM)

commencer

next_state = `PROC_WB

finir

si (état === `PROC_WB)

commencer

next_state = `PROC_FETCH

print_instruction (PC_REG)

finir

finir

tâche print_instruction

entrée [`DATA_INDEX_LIMIT: 0] inst

opcode reg [5: 0]

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] adresse reg immédiat [25: 0]

commencer

// analyse l'instruction

// Type R

{opcode, rs, rt, rd, shamt, funct} = inst

// J'écris

{opcode, rs, rt, immédiat} = inst

// Type J

{opcode, adresse} = inst

$ write ('@% 6dns -> [0X% 08h]', $ time, inst)

case (opcode) // Type R

6'h00: départ

cas (fonction)

6’h20: $ write ('ajouter r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h22: $ write ('sous r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2c: $ write ('mul r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h24: $ write ('et r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h25: $ write ('ou r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h27: $ write ('ni r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2a: $ write ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6h00: $ write ('sll r [% 02d],% 2d, r [% 02d]', rs, shamt, rd)

6’h02: $ write ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6’h08: $ write ('jr r [% 02d]', rs)

par défaut: $ write ('')

endcase

finir

// J'écris

6’h08: $ write ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h1d: $ write ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h0c: $ write ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h0d: $ write ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h0f: $ write ('lui r [% 02d], 0X% 04h', rt, immédiat)

6’h0a: $ write ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h04: $ write ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h05: $ write ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h23: $ write ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

6’h2b: $ write ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, immédiat)

// Type J

6’h02: $ write ('jmp 0X% 07h', adresse)

6’h03: $ write ('jal 0X% 07h', adresse)

6’h1b: $ write ('push')

6’h1c: $ write ('pop')

par défaut: $ write ('')

endcase

$ write (« n»)

finir

tâche finale

module de fin

FAQ

1). Quel est le travail d'une unité de contrôle?

Le travail de l'unité de contrôle est de diriger le flux de données ou d'instructions pour l'exécution par le processeur d'un ordinateur. Il contrôle, gère et coordonne la mémoire principale, l'ALU, les registres, les unités d'entrée et de sortie. Il récupère les instructions et génère des signaux de contrôle pour l'exécution.

2). Quelle est la mémoire de contrôle?

La mémoire de contrôle est généralement RAM ou ROM pour stocker l'adresse et les données du registre de contrôle.

3). Qu'est-ce que l'unité de contrôle Wilkes?

Le séquentiel et circuits combinatoires de l'unité de commande câblée sont remplacées par l'unité de commande Wilkes. Il utilise une unité de stockage pour stocker les séquences d'instructions d'un micro-programme.

4). Qu'est-ce qu'une unité de commande câblée?

L'unité de commande câblée génère les signaux de commande en passant d'un état à un autre état à chaque impulsion d'horloge sans aucun changement physique dans le circuit. La génération des signaux de commande dépend du registre d'instructions, du décodeur et des signaux d'interruption.

5). Quelle est la mémoire de contrôle?

Les informations de l'unité de commande ou les données sont stockées temporairement ou définitivement dans la mémoire de commande.

La mémoire de contrôle est de deux types. Il s'agit de la mémoire vive (RAM) et de la mémoire morte (ROM).

Ainsi, tout est question de définition, de composants, de conception, de diagramme, de fonctions et types d'unités de contrôle . Voici une question pour vous: «À quoi sert le registre d’adresses de contrôle?»