Dans le domaine de l'électronique, le concept le plus crucial sur lequel chaque composant travaille est le « Des portes logiques «. Comme le concept de portes logiques est implémenté dans toutes les fonctionnalités telles que les circuits intégrés, les capteurs, les commutateurs, les microcontrôleurs et les processeurs, le cryptage et le décryptage, etc. En plus de ceux-ci, il existe de nombreuses applications des portes logiques. Il existe de nombreux types de portes logiques telles que Adder, Subtractor, Full Additionneur , Full Subtractor, Half Subtractor et bien d'autres. Ainsi, cet article fournit des informations collectives sur circuit demi soustracteur , table de vérité demi soustracteur , et concepts associés.

Qu'est-ce que Half Subtractor?

Avant de discuter du demi soustracteur, nous devons connaître la soustraction binaire. En soustraction binaire, le processus de soustraction est similaire à la soustraction arithmétique. Dans la soustraction arithmétique, le système numérique de base 2 est utilisé, tandis que dans la soustraction binaire, les nombres binaires sont utilisés pour la soustraction. Les termes résultants peuvent être désignés par la différence et emprunter.

Le demi soustracteur est le plus essentiel circuit logique combinatoire qui est utilisé dans électronique numérique . Fondamentalement, il s'agit d'un appareil électronique ou en d'autres termes, nous pouvons le dire comme un circuit logique. Ce circuit est utilisé pour effectuer la soustraction de deux chiffres binaires. Dans l'article précédent, nous avons déjà discuté les concepts de demi-additionneur et d'un circuit d'additionneur complet qui utilise des nombres binaires pour le calcul. De même, le circuit soustracteur utilise des nombres binaires (0,1) pour la soustraction. Le circuit du demi soustracteur peut être construit avec deux portes logiques, à savoir portes NAND et EX-OR . Ce circuit donne deux éléments tels que la différence ainsi qu'ils empruntent.

Comme dans la soustraction binaire, le chiffre majeur est 1, nous pouvons générer un emprunt tandis que le sous-retrait 1 est supérieur au minuend 0 et pour cette raison, il faudra emprunter. L'exemple suivant donne la soustraction binaire de deux bits binaires.

Premier chiffre | Deuxième chiffre | Différence | Emprunter |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Dans la soustraction ci-dessus, les deux chiffres peuvent être représentés par A et B. Ces deux chiffres peuvent être soustraits et donnent les bits résultants sous forme de différence et d'emprunt.

Lorsque nous observons les deux premières et quatrième lignes, la différence entre ces lignes, puis la différence et l'emprunt sont similaires car la sous-fin est inférieure au minuend. De même, lorsque nous observons la troisième ligne, la valeur minuend est soustraite de la subtrahend. Ainsi, la différence et les bits d'emprunt sont 1 parce que le chiffre de sous-retrait est supérieur au chiffre de minimum.

Ce circuit combinatoire est un outil essentiel pour tout type de circuit numérique pour connaître les combinaisons possibles d'entrées et de sorties. Par exemple, si le soustracteur a deux entrées, les sorties résultantes seront quatre. Le o / p du demi soustracteur est mentionné dans le tableau ci-dessous qui signifiera le bit de différence ainsi que le bit d'emprunt. L’explication de la table de vérité du circuit peut être effectuée en utilisant les portes logiques telles que la porte logique EX-OR et le fonctionnement de la porte ET suivis de la porte NOT.

Résoudre la table de vérité en utilisant K-Map est illustré ci-dessous.

carte demi soustracteur k

Le expression demi-soustracteur en utilisant la table de vérité et la K-map peut être dérivée comme

Différence (D) = ( x’y + xy ')

= x ⊕ y

Emprunter (B) = x’y

Circuit logique

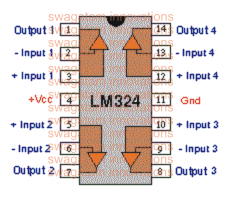

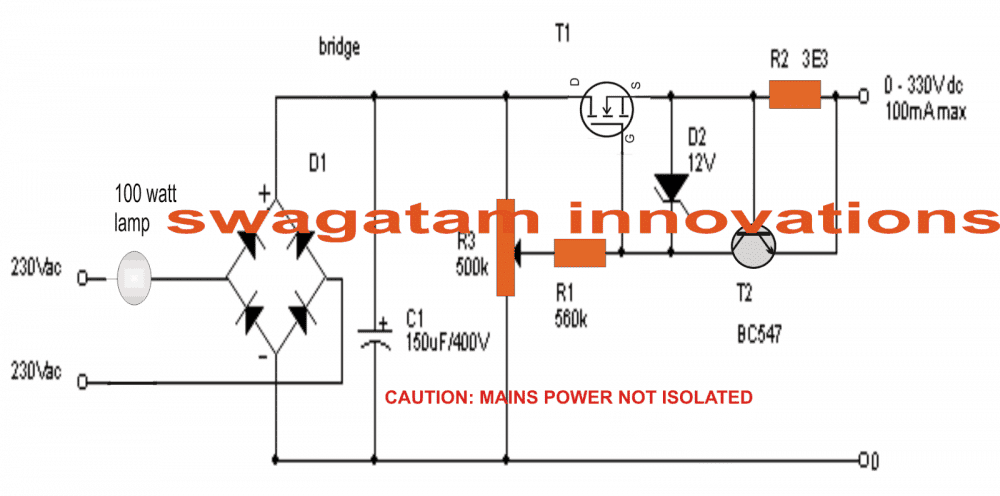

Le circuit logique demi soustracteur peut être expliqué en utilisant les portes logiques:

- 1 porte XOR

- 1 porte PAS

- 1 porte ET

La représentation est

Circuit logique demi soustracteur

Schéma fonctionnel du demi-soustracteur

Le schéma fonctionnel du demi soustracteur est illustré ci-dessus. Il nécessite deux entrées et donne deux sorties. Ici, les entrées sont représentées par A&B et les sorties sont Différence et Emprunt.

Le circuit ci-dessus peut être conçu avec des portes EX-OR et NAND. Ici, la porte NAND peut être construite en utilisant des portes AND et NOT. Nous avons donc besoin de trois portes logiques pour créer un demi-circuit soustracteur à savoir la porte EX-OR, la porte NOT et la porte NAND.

Une combinaison de portes AND et NOT produit une porte combinée différente nommée NAND Gate. La sortie de la porte Ex-OR sera le bit de différence et la sortie de la porte NAND sera le bit d'emprunt pour les mêmes entrées A&B.

AND-Gate

La porte ET est un type de porte logique numérique avec plusieurs entrées et une seule sortie et basée sur les combinaisons d'entrées, elle effectuera la conjonction logique. Lorsque toutes les entrées de cette porte sont hautes, alors la sortie sera élevée sinon la sortie sera basse. Le schéma logique de la porte ET avec table de vérité est illustré ci-dessous.

ET Table de porte et de vérité

PAS de porte

La porte NOT est un type de porte logique numérique avec une seule entrée et en fonction de l'entrée, la sortie sera inversée. Par exemple, lorsque l'entrée de la porte NOT est haute, la sortie sera basse. Le schéma logique de NOT-gate avec la table de vérité est présenté ci-dessous. En utilisant ce type de porte logique, nous pouvons exécuter des portes NAND et NOR.

PAS de porte et table de vérité

Porte Ex-OR

La porte Exclusive-OR ou EX-OR est un type de porte logique numérique avec 2 entrées et une sortie unique. Le fonctionnement de cette porte logique dépend de la porte OU. Si l'une des entrées de cette porte est haute, la sortie de la porte EX-OR sera élevée. Le symbole et la table de vérité de l'EX-OR sont indiqués ci-dessous.

Porte XOR et table de vérité

Circuit demi soustracteur utilisant Nand Gate

La conception du soustracteur peut être effectuée par en utilisant des portes logiques comme la porte NAND et la porte Ex-OR. Afin de concevoir ce circuit de demi soustracteur, nous devons connaître les deux concepts à savoir la différence et l'emprunt.

Circuit demi soustracteur utilisant Nand Gate

Si l'on surveille avec prudence, il est assez clair que la variété d'opérations exécutées par ce circuit qui est précisément liée à l'opération de porte EX-OR. Par conséquent, nous pouvons simplement utiliser la porte EX-OR pour faire la différence. De la même manière, l'emprunt produit par le demi-circuit additionneur peut être simplement atteint en utilisant le mélange de portes logiques comme la porte ET et la porte NON.

Ce HS peut également être conçu en utilisant des portes NOR où il nécessite 5 portes NOR pour la construction. Le demi soustracteur de schéma de circuit utilisant des portes NOR est représenté par:

Demi soustracteur utilisant ni portes

Table de vérité

Premier bit | Deuxième bit | Différence (EX-OR Out) | Emprunter (Sortie NAND) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

Code VHDL et Testbench

Le code VHDL pour le demi soustracteur est expliqué comme suit:

bibliothèque IEEE

utilisez IEEE.STD_LOGIC_1164.ALL

utilisez IEEE.STD_LOGIC_ARITH.ALL

utilisez IEEE.STD_LOGIC_UNSIGNED.ALL

l'entité Half_Sub1 est

Port (a: dans STD_LOGIC

b: dans STD_LOGIC

HS_Diff: sortie STD_LOGIC

HS_Borrow: sur STD_LOGIC)

end Half_Sub1

architecture Le comportement de Half_Sub1 est

commencer

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

Le code testbench pour HS est expliqué comme ci-dessous:

BIBLIOTHÈQUE IEEE

UTILISEZ ieee.std_logic_1164.ALL

ENTITY HS_tb IS

END HS_tb

ARCHITECTURE HS_tb DE HS_tb IS

COMPOSANT HS

PORT (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

COMPOSANT DE FIN

signal a: std_logic: = '0'

signal b: std_logic: = '0'

signal HS_Diff: std_logic

signal HS_Borrow: std_logic

COMMENCER

nouveau: HS PORT MAP (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: processus

commencer

à<= ‘0’

b<= ‘0’

attendez 30 ns

à<= ‘0’

b<= ‘1’

attendez 30 ns

à<= ‘1’

b<= ‘0’

attendez 30 ns

à<= ‘1’

b<= ‘1’

attendre

processus final

FINIR

Soustracteur complet utilisant un demi-soustracteur

Un soustracteur complet est un dispositif combinatoire qui exploite la fonctionnalité de soustraction en utilisant deux bits et qui est un minuend et un subtrahend. Le circuit considère l'emprunt de la sortie précédente et il a trois entrées avec deux sorties. Les trois entrées sont le minuend, le subtrahend et l'entrée reçue de la sortie précédente qui est emprunter et les deux sorties sont la différence et l'emprunt.

Diagramme logique du soustracteur complet

La table de vérité pour soustracteur complet est

| Contributions | Les sorties | |||

| X | Oui | Yin | FS_Diff | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Avec la table de vérité ci-dessus, le schéma logique et le schéma des circuits pour la mise en œuvre d'un soustracteur complet utilisant des demi soustracteurs est présenté ci-dessous:

Soustracteur complet utilisant HS

Avantages et limites du demi-soustracteur

Les avantages du demi-soustracteur sont:

- La mise en œuvre et la construction de ce circuit est simple et facile

- Ce circuit consomme une puissance minimale dans le traitement du signal numérique

- les fonctionnalités de calcul peuvent être exécutées à des vitesses améliorées

Les limites de ce circuit combinatoire sont:

Même s'il existe de nombreuses applications du demi-soustracteur dans de nombreuses opérations et fonctionnalités, il existe peu de limitations et celles-ci sont:

- Les circuits demi-soustracteurs n'accepteront pas le «Borrow-in» des sorties précédentes où c'est l'inconvénient crucial de ce circuit

- Comme de nombreuses applications en temps réel fonctionnent sur la soustraction d'un grand nombre de bits, les demi-soustracteurs ne détiennent aucune capacité de soustraction de nombreux bits

Applications du demi-soustracteur

Les applications du demi soustracteur comprennent les suivantes.

- Le demi soustracteur est utilisé pour réduire la force des signaux audio ou radio

- Ça peut être utilisé dans les amplificateurs pour réduire la distorsion sonore

- Le demi soustracteur est utilisé en ALU du processeur

- Il peut être utilisé pour augmenter et diminuer les opérateurs et calcule également les adresses

- Un demi-soustracteur est utilisé pour soustraire les numéros de colonne les moins significatifs. Pour la soustraction de nombres à plusieurs chiffres, il peut être utilisé pour le LSB.

Par conséquent, à partir de la théorie du demi-soustracteur ci-dessus, nous pouvons enfin conclure qu'en utilisant ce circuit, nous pouvons soustraire un bit binaire d'un autre pour fournir les sorties telles que la différence et l'emprunt. De même, nous pouvons concevoir un demi soustracteur en utilisant un circuit de portes NAND ainsi que des portes NOR. Les autres concepts à connaître sont ce qu'est le code verilog demi soustracteur et comment le diagramme schématique RTL peut-il être dessiné?