La fonction principale du générateur de parité et du vérificateur de parité est de détecter les erreurs de transmission de données et ce concept a été introduit en 1922. Dans la technologie RAID, le bit de parité et le vérificateur de parité sont utilisés pour se prémunir contre la perte de données. Le bit de parité est un bit supplémentaire qui est défini du côté transmission sur «0» ou «1», il est utilisé pour détecter une seule erreur sur un seul bit et c'est la méthode la plus simple pour détecter les erreurs. Il existe différents types de codes de détection d'erreurs utilisés pour détecter les erreurs: parité, compteur d'anneau, code de parité de bloc, code de Hamming, biquinaire, etc. La brève explication sur le bit de parité, la parité Générateur et le vérificateur sont expliqués ci-dessous.

Qu'est-ce que le bit de parité?

Définition: Le bit de parité ou le bit de contrôle sont les bits ajoutés au code binaire pour vérifier si le code particulier est en parité ou non, par exemple, si le code est en parité paire ou si la parité impaire est vérifiée par ce bit de contrôle ou ce bit de parité. La parité n'est rien d'autre que le nombre de 1 et il existe deux types de bits de parité: les bits pairs et les bits impairs.

Dans le bit de parité impair, le code doit être dans un nombre impair de 1, par exemple, nous prenons le code à 5 bits 100011, ce code est dit être une parité impaire car il y a trois nombres de 1 dans le code que nous avons pris . En bit de parité pair, le code doit être en nombre pair de 1, par exemple, nous prenons le code à 6 bits 101101, ce code est dit à parité paire car il y a quatre nombres de 1 dans le code que nous avons pris

Qu'est-ce que le générateur de parité?

Définition: Le générateur de parité est un circuit combiné au niveau de l'émetteur, il prend un message d'origine en entrée et génère le bit de parité pour ce message et l'émetteur dans ce générateur transmet des messages avec son bit de parité.

Types de générateur de parité

La classification de ce générateur est indiquée dans la figure ci-dessous

générateur de types de parité

Générateur de parité paire

Le générateur de parité paire maintient les données binaires en nombre pair de 1, par exemple, les données prises sont en nombre impair de 1, ce générateur de parité paire va maintenir les données en nombre pair de 1 en ajoutant le 1 supplémentaire à l'impair nombre de 1. Il s'agit également d'un circuit combinatoire dont la sortie dépend des données d'entrée données, ce qui signifie que les données d'entrée sont des données binaires ou un code binaire donné pour le générateur de parité.

Considérons trois données binaires d'entrée, que trois bits sont considérés comme A, B et C. Nous pouvons écrire 23combinaisons utilisant les trois données binaires d'entrée qui vont de 000 à 111 (0 à 7), huit combinaisons au total seront obtenues à partir des trois données binaires d'entrée que nous avons considérées. La table de vérité du générateur de parité paire pour trois données binaires d'entrée est présentée ci-dessous.

0 0 0 - Dans ce code binaire d’entrée, la parité paire est considérée comme «0» car l’entrée est déjà en parité paire, il n’est donc pas nécessaire d’ajouter à nouveau la parité paire pour cette entrée.

0 0 1 - - Dans ce code binaire d’entrée, il n’y a qu’un seul nombre de «1» et ce nombre unique de «1» est un nombre impair de «1». Si un nombre impair de «1» est présent, alors le générateur de parité paire doit générer un autre «1» pour en faire une parité paire, de sorte que la parité paire est considérée comme 1 pour faire du code 0 0 1 une parité paire.

0 1 0 - Ce bit est en parité impaire, donc la parité paire est considérée comme 1 pour transformer le code 0 1 0 en parité paire.

0 1 1 - Ce bit est déjà en parité paire, donc la parité paire est prise égale à 0 pour faire du code 0 1 1 une parité paire.

1 0 0 - Ce bit est en parité impaire, donc la parité paire est considérée comme 1 pour faire du code 1 0 0 une parité paire.

1 0 1 - Ce bit est déjà en parité paire, donc la parité paire est prise égale à 0 pour faire du code 1 0 1 une parité paire.

1 1 0 - Ce bit est également en parité paire, de sorte que la parité paire est prise égale à 0 pour faire du code 1 1 0 une parité paire.

1 1 1 - Ce bit est en parité impaire, donc la parité paire est considérée comme 1 pour rendre le code 1 1 1 en parité paire.

Table de vérité du générateur de parité paire

| A B C | Parité paire |

| 0 0 0 | 0 |

| 0 0 1 | 1 |

| 0 1 0 | 1 |

| 0 1 1 | 0 |

| 1 0 0 | 1 |

| 1 0 1 | 0 |

| 1 1 0 | 0 |

| 1 1 1 | 1 |

La simplification de la carte karnaugh (k-map) pour la parité paire d'entrée à trois bits est

k-map-for-pair-parité-générateur

À partir de la table de vérité de parité paire ci-dessus, l'expression simplifiée du bit de parité s'écrit

L'expression de parité paire implémentée en utilisant deux portes Ex-OR et le diagramme logique de cette parité paire en utilisant l'Ex-OR porte logique est illustré ci-dessous.

circuit-logique-parité-paire

De cette manière, le générateur de parité paire génère un nombre pair de 1 en prenant les données d'entrée.

Générateur de parité impaire

Le générateur de parité impaire maintient les données binaires dans un nombre impair de 1, par exemple, les données prises sont en nombre pair de 1, ce générateur de parité impaire va maintenir les données sous la forme d'un nombre impair de 1 en ajoutant le 1 supplémentaire à le nombre pair de 1. Il s'agit du circuit combinatoire dont la sortie dépend toujours des données d'entrée données. S'il existe un nombre pair de 1, seul le bit de parité est ajouté pour transformer le code binaire en un nombre impair de 1.

Considérons trois données binaires d'entrée, que trois bits sont considérés comme A, B et C. La table de vérité du générateur de parité impaire pour trois données binaires d'entrée est indiquée ci-dessous.

0 0 0 - Dans ce code binaire d’entrée, la parité impaire est considérée comme «1» car l’entrée est en parité paire.

0 0 1 - Cette entrée binaire est déjà en parité impaire, donc la parité impaire est considérée comme 0.

0 1 0 - Cette entrée binaire est également en parité impaire, donc la parité impaire est prise égale à 0.

0 1 1 - Ce bit est en parité paire, donc la parité impaire est prise comme 1 pour rendre le code 0 1 1 en parité impaire.

1 0 0 - Ce bit est déjà en parité impaire, donc la parité impaire est prise égale à 0 pour faire du code 1 0 0 une parité impaire.

1 0 1 - Ce bit d'entrée est en parité paire, donc la parité impaire est prise comme 1 pour rendre le code 1 0 1 en parité impaire.

1 1 0 - Ce bit est en parité paire, donc la parité impaire est considérée comme 1.

1 1 1 - Ce bit d'entrée est en parité impaire, donc la parité impaire est considérée comme o.

Tableau de vérité du générateur de parité impaire

| A B C | Parité impaire |

| 0 0 0 | 1 |

| 0 0 1 | 0 |

| 0 1 0 | 0 |

| 0 1 1 | 1 |

| 1 0 0 | 0 |

| 1 0 1 | 1 |

| 1 1 0 | 1 |

| 1 1 1 | 0 |

La simplification de la carte de Kavanaugh (k-map) pour la parité impaire d'entrée à trois bits est

k-map-for-impair-parity-generator

À partir de la table de vérité de parité impaire ci-dessus, l'expression simplifiée du bit de parité s'écrit

Le schéma logique de ce générateur de parité impaire est illustré ci-dessous.

circuit logique

De cette manière, le générateur de parité impaire génère un nombre impair de 1 en prenant les données d'entrée.

Qu'est-ce que le contrôle de parité?

Définition: Le circuit combinatoire au niveau du récepteur est le vérificateur de parité. Ce vérificateur prend le message reçu avec le bit de parité en entrée. Il donne la sortie '1' s'il y a une erreur trouvée et donne la sortie '0' si aucune erreur n'est trouvée dans le message, y compris le bit de parité.

Types de vérificateur de parité

La classification du vérificateur de parité est indiquée dans la figure ci-dessous

vérificateur de types de parité

Vérificateur de parité paire

Dans le vérificateur de parité paire, si le bit d’erreur (E) est égal à «1», alors nous avons une erreur. Si le bit d'erreur E = 0 indique qu'il n'y a pas d'erreur.

Bit d'erreur (E) = 1, une erreur se produit

Bit d'erreur (E) = 0, pas d'erreur

Le circuit du vérificateur de parité est illustré dans la figure ci-dessous

circuit logique

Vérificateur de parité impaire

Dans le vérificateur de parité impaire, si un bit d’erreur (E) est égal à «1», cela indique qu’il n’ya pas d’erreur. Si un bit d'erreur E = 0 indique alors qu'il y a une erreur.

Bit d'erreur (E) = 1, pas d'erreur

Bit d'erreur (E) = 0, une erreur se produit

Le vérificateur de parité ne pourra pas détecter s’il y a des erreurs dans plus de «1» bit et la correction des données n’est pas non plus possible, ce sont les principaux inconvénients du vérificateur de parité.

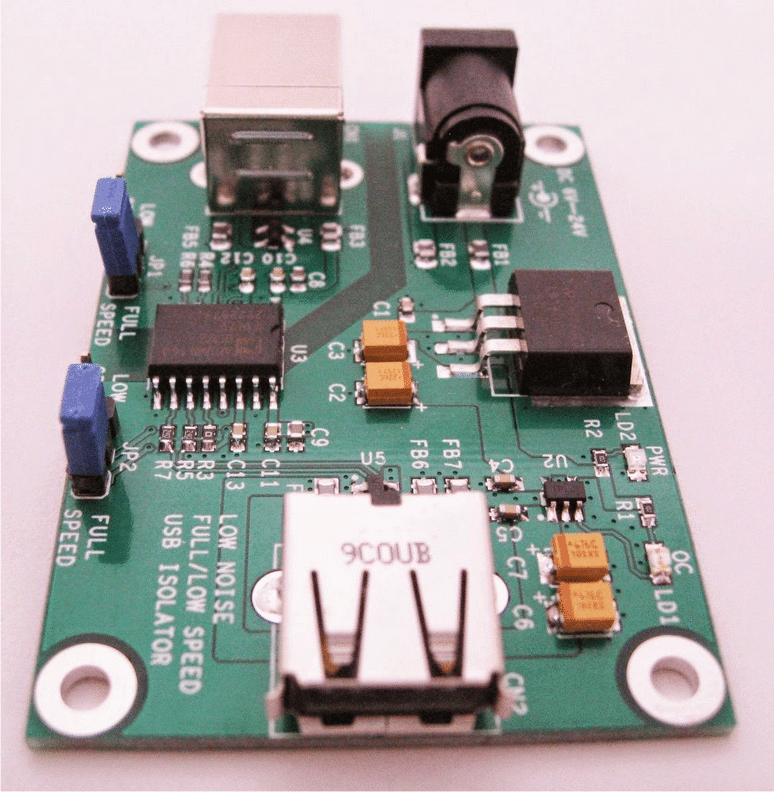

Générateur / vérificateur de parité utilisant des IC

L'IC 74180 remplit la fonction de génération de parité ainsi que de vérification. Le générateur / vérificateur de parité à 9 bits (8 bits de données, 1 bit de parité) est illustré dans la figure ci-dessous.

ic-74180

L'IC 74180 contient huit bits de données (X0à X7), VDC,entrée paire, entrée impaire, sept sorties, sortie impaire S et broche de masse.

Si les entrées paires et impaires données sont toutes les deux hautes (H), alors les sorties paires et impaires sont toutes les deux basses (L), de même, si les entrées données sont toutes les deux basses (L), alors les sorties paires et impaires deviennent toutes deux élevées ( H).

Avantages de la parité

Les avantages de la parité sont

- Simplicité

- Facile à utiliser

Applications de parité

Les applications de la parité sont

- Dans systèmes numériques et de nombreuses applications matérielles, cette parité est utilisée

- Le bit de parité est également utilisé dans Small Computer System Interface (SCSI) et également dans Peripheral Component Interconnect (PCI) pour détecter les erreurs

FAQ

1). Quelle est la différence entre le générateur de parité et le vérificateur de parité?

Le générateur de parité génère le bit de parité dans l'émetteur et le vérificateur de parité vérifie le bit de parité dans le récepteur.

2). Que signifie pas de parité?

Lorsque les bits de parité ne sont pas utilisés pour vérifier les erreurs, le bit de parité est dit non-parité ou pas de parité ou absence de parité.

3). Quelle est la valeur de parité?

Le concept de valeur de parité utilisé à la fois pour les matières premières et les titres et le terme désigne le moment où la valeur des deux actifs est égale.

4). Pourquoi avons-nous besoin d'un vérificateur de parité?

Le vérificateur de parité est nécessaire pour détecter les erreurs de communication et également dans les périphériques de stockage de mémoire, le vérificateur de parité est utilisé pour les tests.

5). Comment le bit de parité peut-il détecter une unité de données endommagée?

Le bit redondant dans cette technique est appelé un bit de parité, il détecte une unité de données endommagée lorsqu'une erreur se produit lors de la transmission des données.

Dans cet article, comment le parité le générateur et le vérificateur génèrent et vérifient le bit et ses types, les circuits logiques, les tables de vérité et les expressions k-map sont brièvement discutés. Voici une question pour vous, comment calculez-vous la parité paire et impaire?