L'augmentation de la vitesse d'exécution du programme augmente par conséquent la vitesse de le processeur. Il existe de nombreuses méthodes, à la fois la mise en œuvre matérielle et l'architecture logicielle, pour augmenter la vitesse d'exécution. Il a été observé qu'en exécutant des instructions simultanément, le temps nécessaire à l'exécution peut être réduit. Le concept de parallélisme dans programmation a été proposé. Selon cela, plus d'une instruction peut être exécutée par cycle d'horloge. Ce concept peut être mis en pratique par un programmeur à travers diverses techniques telles que Pipeline, unités d'exécution multiples et cœurs multiples . Parmi toutes ces méthodes de parallélisme, le pipelining est le plus couramment pratiqué. Alors, comment une instruction peut-elle être exécutée dans la méthode de pipelining? Comment augmente-t-il la vitesse d'exécution?

Qu'est-ce que le pipelining?

Pour saisir le concept de pipelining, regardons au niveau racine de la façon dont le programme est exécuté. L'instruction est le plus petit paquet d'exécution d'un programme. Chaque instruction contient une ou plusieurs opérations. Les processeurs scalaires simples exécutent une ou plusieurs instructions par cycle d'horloge, chaque instruction ne contenant qu'une seule opération. Les instructions sont exécutées comme une séquence de phases, pour produire les résultats attendus. Cette séquence est donnée ci-dessous

Séquence d'exécution des instructions

- IF: récupère l'instruction dans le registre d'instructions.

- ID: Instruction Decode, décode l'instruction pour l'opcode.

- AG: Address Generator, génère l'adresse.

- DF: Data Fetch, récupère les opérandes dans le registre de données.

- EX: Exécution, exécute l'opération spécifiée.

- WB: réécrire, réécrit le résultat dans le registre.

Toutes les instructions ne nécessitent pas toutes les étapes ci-dessus, mais la plupart le font. Ces étapes utilisent différentes fonctions matérielles. En pipelining, ces différentes phases sont effectuées simultanément. Dans le pipeline, ces phases sont considérées comme indépendantes entre les différentes opérations et peuvent se chevaucher. Ainsi, plusieurs opérations peuvent être effectuées simultanément, chaque opération étant dans sa propre phase indépendante.

Instruction Pipelining

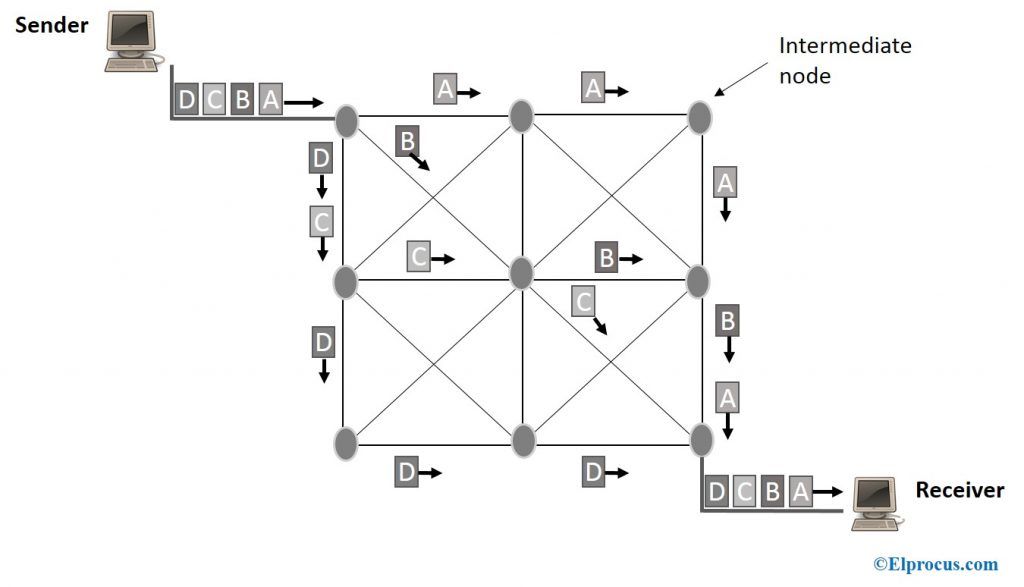

Voyons comment les instructions sont traitées dans le pipelining. Cela peut être facilement compris par le diagramme ci-dessous.

Instruction Pipelining

Supposons que les instructions soient indépendantes. Dans un processeur de pipelining simple, à un instant donné, il n'y a qu'une seule opération dans chaque phase. La phase initiale est la phase IF. Ainsi, au premier cycle d'horloge, une opération est récupérée. Lorsque la prochaine impulsion d'horloge arrive, la première opération entre dans la phase ID laissant la phase IF vide. Maintenant, cette phase vide est allouée à l'opération suivante. Ainsi, pendant la deuxième impulsion d'horloge, la première opération est dans la phase d'identification et la deuxième opération est dans la phase IF.

Pour le troisième cycle, la première opération sera en phase AG, la deuxième opération sera en phase ID et la troisième opération sera en phase IF. De cette manière, les instructions sont exécutées simultanément et après six cycles, le processeur sortira une instruction complètement exécutée par cycle d'horloge.

Cette instruction a-t-elle été exécutée séquentiellement, initialement la première instruction doit passer par toutes les phases, puis l'instruction suivante serait récupérée? Ainsi, pour l'exécution de chaque instruction, le processeur nécessiterait six cycles d'horloge. Mais dans un processeur en pipeline, comme l'exécution des instructions a lieu simultanément, seule l'instruction initiale nécessite six cycles et toutes les instructions restantes sont exécutées comme une pour chaque cycle, réduisant ainsi le temps d'exécution et augmentant la vitesse du processeur.

Architecture de pipelining

Le parallélisme peut être obtenu avec les techniques matérielles, compilateurs et logicielles. Exploiter le concept de pipelining en l'architecture des ordinateurs de nombreuses unités de traitement sont interconnectées et fonctionnent simultanément. Dans l'architecture de processeur en pipeline, des unités de traitement séparées sont fournies pour les entiers et les instructions à virgule flottante. Alors que dans l'architecture séquentielle, une seule unité fonctionnelle est fournie.

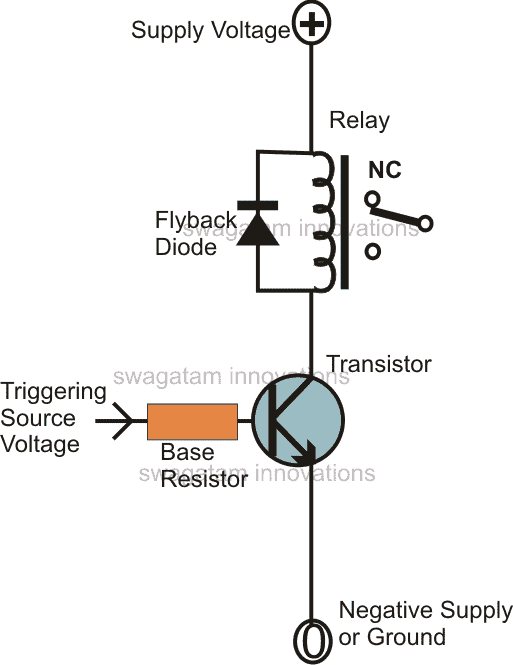

Unité de traitement en pipeline

Dans le pipeline statique, le processeur doit passer l'instruction à travers toutes les phases du pipeline indépendamment de l'exigence de l'instruction. Dans un processeur de pipeline dynamique, une instruction peut contourner les phases en fonction de ses besoins, mais doit se déplacer dans un ordre séquentiel. Dans un processeur de pipeline dynamique complexe, l'instruction peut contourner les phases et choisir les phases dans le désordre.

Pipeline dans les processeurs RISC

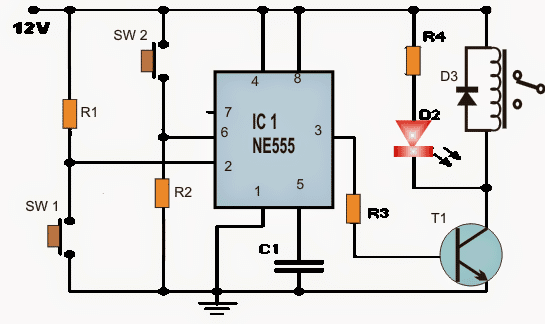

Le plus populaire Architecture RISC Le processeur ARM suit le pipelining à 3 et 5 étages. Dans le pipelining en 3 étapes, les étapes sont: Extraire, Décoder et Exécuter. Ce pipelining a 3 cycles de latence, car une instruction individuelle prend 3 cycles d'horloge pour se terminer.

Pipelining ARM 3 étapes

Pour une mise en œuvre correcte du pipeline, l'architecture matérielle doit également être mise à niveau. Le matériel pour le pipelining à 3 étages comprend une banque de registres, une ALU, un shifter Barrel, un générateur d'adresses, un incrémenteur, un décodeur d'instructions et des registres de données.

Chemin de données de pipetage ARM à 3 étapes

En 5 étapes de pipelining, les étapes sont: Fetch, Decode, Execute, Buffer / data et Write back.

Risques de pipelinage

Dans un programme informatique typique, en plus des instructions simples, il existe des instructions de branchement, des opérations d'interruption, des instructions de lecture et d'écriture. Le pipelining ne convient pas à toutes sortes d'instructions. Lorsque certaines instructions sont exécutées dans le pipeline, elles peuvent bloquer le pipeline ou le rincer totalement. Ce type de problèmes causés lors de la tuyauterie est appelé risques de pipelining.

Dans la plupart des programmes informatiques, le résultat d'une instruction est utilisé comme opérande par l'autre instruction. Lorsque de telles instructions sont exécutées en pipelining, une panne se produit car le résultat de la première instruction n'est pas disponible lorsque l'instruction deux commence à collecter des opérandes. Ainsi, l'instruction 2 doit se bloquer jusqu'à ce que l'instruction 1 soit exécutée et que le résultat soit généré. Ce type de danger est appelé danger de pipelining en lecture-après-écriture.

Risque de pipelining lecture après écriture

L'exécution des instructions de branchement entraîne également un risque de pipelining. Instructions de branche lors de l'exécution en pipelining affecte les étapes de récupération des instructions suivantes.

Comportement des branches pipelinées

Avantages du pipelining

- Le débit d'instruction augmente.

- L'augmentation du nombre d'étages de pipeline augmente le nombre d'instructions exécutées simultanément.

- Une ALU plus rapide peut être conçue lorsque le pipelining est utilisé.

- Le processeur pipeliné fonctionne à des fréquences d’horloge plus élevées que la RAM.

- Le pipelining augmente les performances globales du processeur.

Inconvénients du pipelining

- La conception du processeur en pipeline est complexe.

- La latence des instructions augmente dans les processeurs en pipeline.

- Le débit d'un processeur en pipeline est difficile à prévoir.

- Plus le pipeline est long, pire le problème du danger pour les instructions de branchement.

Le pipelining bénéficie de toutes les instructions qui suivent une séquence d'étapes similaire pour l'exécution. Les processeurs qui ont des instructions complexes dans lesquelles chaque instruction se comporte différemment des autres sont difficiles à canaliser. Les transformateurs ont des outils raisonnables avec 3 ou 5 étapes du pipeline car à mesure que la profondeur du pipeline augmente, les risques qui y sont liés augmentent. Nommez certains des processeurs en pipeline avec leur stade de pipeline?