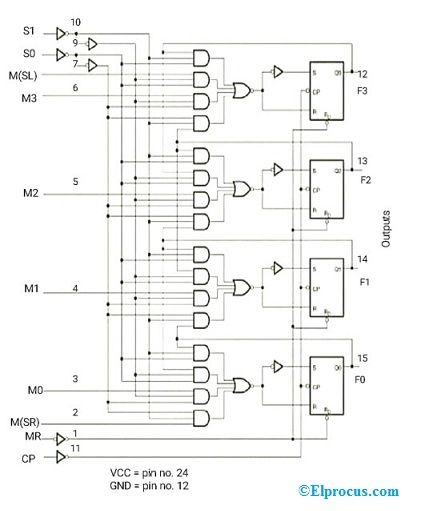

En règle générale, un registre peut être défini comme un périphérique utilisé pour stocker les données binaires, mais si vous souhaitez stocker plusieurs bits de données, un ensemble de bascules connectées en série est utilisé. Les données qui sont stockées dans les registres peuvent être décalées en utilisant des registres à décalage du côté droit ou du côté gauche en fournissant des impulsions CLK. Registre à décalage est un groupe de tongs utilisé pour stocker plusieurs bits de données. De même, un registre à décalage à n bits peut être formé en connectant simplement n bascules là où chaque bascule stocke simplement un seul bit de données. Une fois que le registre décale les bits vers la droite, il s'agit du registre à décalage droit, tandis que s'il se décale vers la gauche, il est appelé registre à décalage gauche. Cet article traite d'un aperçu de l'un des types de registre à décalage, à savoir le registre à décalage série en parallèle ou Registre à décalage SIPO .

Qu'est-ce que le registre à décalage SIPO ?

Le registre à décalage qui permet une sortie parallèle d'entrée série est appelé registre à décalage SIPO. Dans le registre SIPO, le terme SIPO signifie entrée série sortie parallèle. Dans ce type de registre à décalage, les données d'entrée sont données bit à bit en série. Pour chaque impulsion d'horloge, les données d'entrée de tous les FF peuvent être décalées d'une seule position. L'o/p à chaque bascule peut être reçu en parallèle.

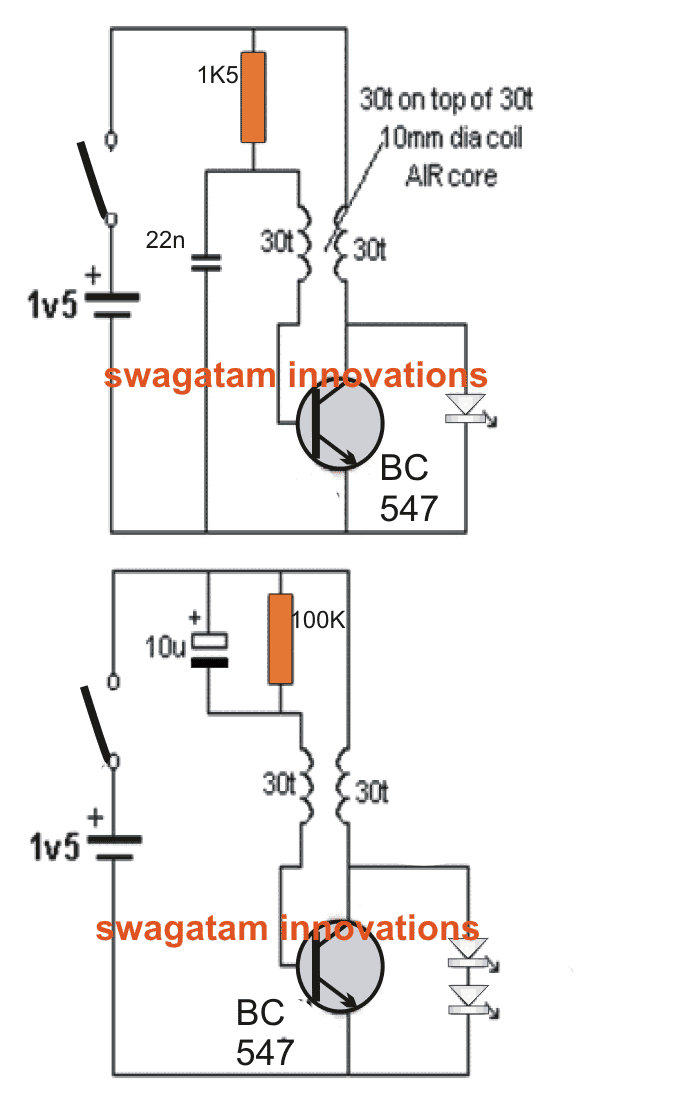

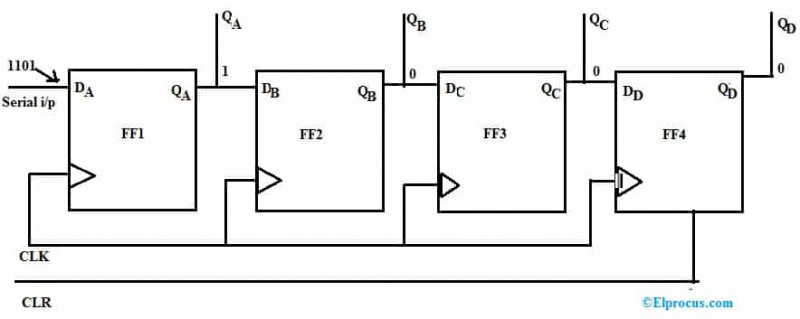

Schéma

La Schéma du circuit du registre à décalage SISO est illustré ci-dessous. Ce circuit peut être construit avec 4 bascules D qui sont connectées comme indiqué sur le schéma où le signal CLR est donné en plus du signal CLK à tous les FF ou les RESET. Dans le circuit ci-dessus, la première sortie FF est donnée à la deuxième entrée FF. Ces quatre bascules D sont connectées les unes aux autres en série car le même signal CLK est donné à chaque bascule.

Fonctionnement du registre à décalage SIPO

Le fonctionnement du registre à décalage SIPO est ; qu'il prend l'entrée de données série de la première bascule du côté gauche et génère une sortie de données parallèle. Le circuit de registre à décalage SIPO 4 bits est illustré ci-dessous. Le fonctionnement de ce registre à décalage est que toutes les bascules du circuit de FF1 à FF4 doivent d'abord être RÉINITIALISÉES afin que toutes les sorties des FF comme QA à QD soient au niveau logique zéro, de sorte qu'il n'y a pas de sortie de données parallèle.

La construction du registre à décalage SIPO est illustrée ci-dessus. Dans le schéma, la première sortie de bascule 'QA' est connectée à la deuxième entrée de bascule 'DB'. La sortie de la deuxième bascule 'QB' est connectée à l'entrée DC de la troisième bascule, et la sortie de la troisième bascule 'QC' est connectée à l'entrée de la quatrième bascule 'DD'. Ici, QA, QB, QC et QD sont des sorties de données.

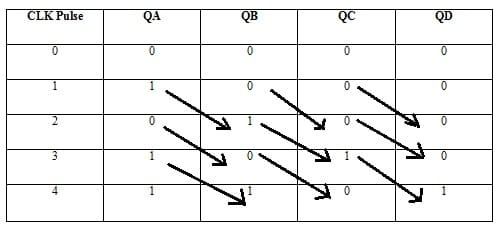

Initialement, toute la sortie deviendra nulle donc sans impulsion CLK ; toutes les données deviendront nulles. Prenons un exemple d'entrée de données 4 bits comme 1101. Si nous appliquons la première impulsion d'horloge '1' à la première bascule, les données à entrer dans le FF et QA deviennent '1', et restant toutes les sorties comme QB , QC et QD deviendront nuls. Ainsi, la première sortie de données est '1000'

Si nous appliquons la deuxième impulsion d'horloge en tant que '0' à la première bascule, QA devient '0', QB devient '0', QC devient '0' et QD devient '0'. Ainsi, la deuxième sortie de données deviendra « 0100 » en raison du processus de décalage vers la droite.

Si nous appliquons la troisième impulsion d'horloge comme '1' à la première bascule, QA devient '1', QB devient '0', QC devient '1' et QD devient '0'. Ainsi, la troisième sortie de données deviendra « 1011 » en raison du processus de décalage vers la droite.

Si nous appliquons la quatrième impulsion d'horloge en tant que '1' à la première bascule, QA devient '1', QB devient '1', QC devient '0' et QD devient '1'. Ainsi, la troisième sortie de données deviendra « 1101 » en raison du processus de décalage vers la droite.

Table de vérité du registre à décalage SIPO

La table de vérité du registre à décalage SIPO est présentée ci-dessous.

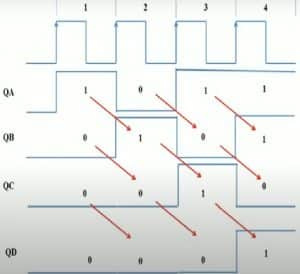

Chronogramme

La chronogramme du registre à décalage SIPO est illustré ci-dessous.

Ici, nous utilisons un signal CLK i/p à front montant. Dans une première impulsion d'horloge, les données d'entrée deviennent QA = '1' et toutes les autres valeurs telles que QB, QC et QD deviennent '0'. Ainsi, la sortie deviendra '1000'. Dans la deuxième impulsion d'horloge, la sortie deviendra '0101'. Dans la troisième impulsion d'horloge, la sortie deviendra '1010' et dans la quatrième impulsion d'horloge, la sortie deviendra '1101'.

Code Verilog du registre à décalage SIPO

Le code Verilog pour le registre à décalage SIPO est indiqué ci-dessous.

module sipomod(clk, clear, si, po);

entrée clk, si, clair ;

sortie [3:0] po ;

reg [3:0] tmp ;

reg [3:0] po ;

toujours @(posege clk)

commencer

Si clair)

tmp <= 4'b0000 ;

autre

tmp <= tmp << 1 ;

tmp[0] <= oui ;

po = tmp ;

fin

module final

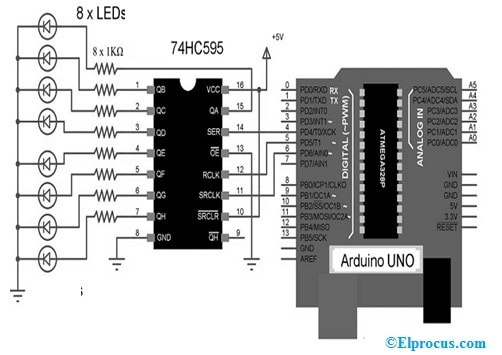

74HC595 Circuit de registre à décalage IC SIPO et son fonctionnement

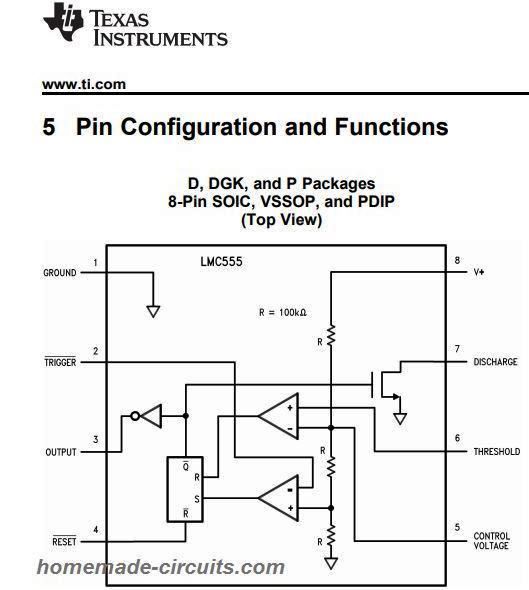

Un circuit intégré 74HC595 est un registre à décalage série 8 bits en sortie parallèle, il utilise donc des entrées en série et fournit des sorties parallèles. Ce circuit intégré comprend 16 broches et est disponible dans différents packages tels que SOIC, DIP, TSSOP et SSOP.

La configuration des broches du 74HC595 est illustrée ci-dessous où chaque broche est décrite ci-dessous.

Broches 1 à 7 & 15 (QB à QH & QA): Ce sont les broches o/p qui sont utilisées pour connecter des périphériques de sortie tels que des écrans à 7 segments et des LED.

Broche 8 (GND): Cette broche GND est simplement connectée à la broche GND de l'alimentation du microcontrôleur.

Pin9 (QH): Cette broche est utilisée pour se connecter à la broche SER d'un CI différent et donner le même signal CLK aux deux CI afin qu'ils fonctionnent comme un seul CI comprenant 16 sorties.

Broche16 (Vcc): Cette broche est utilisée pour se connecter au microcontrôleur sinon alimentation car il s'agit d'un circuit intégré de niveau logique 5V.

Pin14 (BE): C'est la broche Serial i/p où les données sont entrées en série sur cette broche.

Broche 11 (SRCLK): C'est la broche CLK du registre à décalage qui fonctionne comme le CLK pour le registre à décalage car le signal CLK est donné tout au long de cette broche.

Broche 12 (RCLK): C'est la broche Register CLK qui est utilisée pour observer o/ps sur les appareils qui sont connectés à ces CI.

Broche 10 (SRCLR): Il s'agit de la broche CLR du registre à décalage. Cette broche est principalement utilisée lorsque nous devons effacer le stockage du registre.

Broche 13 (OE) : Il s'agit de la broche d'activation o/p. Une fois que cette broche est réglée sur HIGH, le registre à décalage est réglé sur une condition d'impédance élevée et les o/ps ne sont pas transmis. Si nous réglons cette broche au niveau bas, nous pouvons obtenir le o/ps.

74HC595 IC Travail

Le schéma de circuit du circuit intégré 74HC595 pour le contrôle des LED est illustré ci-dessous. Les 3 broches du registre à décalage doivent être connectées à Arduino comme les broches 11, 12 et 14. Les huit LED seront simplement connectées à ce circuit intégré de registre à décalage.

Les composants requis pour concevoir ce circuit comprennent principalement un circuit intégré de registre à décalage 74HC595, Arduino UNO, une alimentation 5V, une planche à pain, 8 LED, des résistances 1KΩ - 8 et des fils de connexion.

Tout d'abord, la broche Serial i/p du registre à décalage doit se connecter à la broche 4 d'Arduino Uno. Après cela, connectez les broches CLK et de verrouillage comme les broches 11 et 12 d'IC aux broches 5 et 6 d'Arduino Uno respectivement. Les LED sont connectées à l'aide de résistances de limitation de courant de 1KΩ aux broches 8-o/p du CI. Une alimentation 5V séparée est utilisée pour 74HC595 IC avec GND commun à Arduino avant de fournir 5V à partir d'Arduino.

Code

Le code simple pour activer 8 LEDs ON en série est illustré ci-dessous.

int verrouPin = 5 ;

int clkPin = 6 ;

int dataPin = 4;

octet LED = 0 ;

void setup()

{

Série.begin(9600);

pinMode(latchPin, OUTPUT);

pinMode(dataPin, OUTPUT);

pinMode(clkPin, SORTIE);

}

boucle vide ()

{

entier je=0 ;

DEL = 0 ;

shiftLED();

retard (500);

pour (i = 0; i < 8; i++)

{

bitSet(DEL, je);

Serial.println(DEL);

shiftLED();

retard (500);

}

}

annuler shiftLED()

{

digitalWrite(latchPin, LOW);

shiftOut(dataPin, clkPin, MSBFIRST, LED);

digitalWrite(latchPin, HIGH);

}

Le fonctionnement de ce circuit de registre à décalage est que, dans un premier temps, toutes les 8 LED seront éteintes car la LED variable d'octet est définie sur zéro. Maintenant, chaque bit est mis à 1 avec la fonction 'bitSet' et est décalé avec la fonction 'shiftOut'. De même, chaque LED sera allumée dans la même série. Si vous souhaitez éteindre la LED, vous pouvez utiliser la fonction 'bitClear'.

Le circuit intégré de registre à décalage 74HC595 est utilisé dans différentes applications telles que les serveurs, le contrôle des LED, le contrôle industriel, les appareils électroniques, les commutateurs de réseau, etc.

Applications

La applications du registre à décalage à sortie parallèle à entrée série est illustré ci-dessous.

- Généralement, le registre à décalage est utilisé pour stocker des données temporaires, utilisé comme un anneau & Johnson Compteur de bagues .

- Ceux-ci sont utilisés pour le transfert de données et la manipulation.

- Ces bascules sont principalement utilisées dans les lignes de communication lorsqu'un démultiplexage de la ligne de données en plusieurs lignes parallèles est nécessaire car ce registre à décalage est utilisé pour changer les données de série en parallèle.

- Ceux-ci sont utilisés pour le cryptage et le décryptage des données.

- Ce registre à décalage est utilisé dans CDMA pour générer un code PN ou un pseudo numéro de séquence de bruit.

- Nous pouvons les utiliser pour suivre nos données !

- Le registre à décalage SIPO est utilisé dans diverses applications numériques pour la conversion de données.

- Parfois, ce type de registre à décalage est simplement connecté au microprocesseur une fois que des broches GPIO supplémentaires sont nécessaires.

- L'application pratique de ce registre à décalage SIPO est de donner les données de sortie du microprocesseur à un indicateur de panneau à distance.

Voici donc un aperçu du SIPO registre à décalage – circuit, fonctionnement, table de vérité et chronogramme avec applications. Les composants de registre à décalage SIPO les plus fréquemment utilisés sont 74HC595, 74LS164, 74HC164/74164, SN74ALS164A, SN74AHC594, SN74AHC595 et CD4094. Ces registres sont très rapides à utiliser, les données peuvent être converties très facilement de série en parallèle et leur conception est simple. Voici une question pour vous, qu'est-ce que le registre à décalage PISO.