L'architecture du jeu d'instructions ou du jeu d'instructions est la structure de l'ordinateur qui fournit des commandes à l'ordinateur pour guider l'ordinateur pour le traitement de la manipulation des données. Le jeu d'instructions comprend des instructions, des modes d'adressage, des types de données natifs, des registres, des interruptions, la gestion des exceptions et l'architecture de la mémoire. Le jeu d'instructions peut être émulé dans le logiciel à l'aide d'un interpréteur ou intégré au matériel du processeur. L'architecture du jeu d'instructions peut être considérée comme une frontière entre le logiciel et le matériel. Classification des microcontrôleurs et les microprocesseurs peuvent être réalisés sur la base de l'architecture du jeu d'instructions RISC et CISC.

Jeu d'instructions du processeur

Le jeu d'instructions spécifie la fonctionnalité du processeur, y compris les opérations prises en charge par le processeur, les mécanismes de stockage du processeur et la manière de compiler les programmes vers le processeur.

Qu'est-ce que RISC et CISC?

Le RISC et CISC peut être développé comme suit:

RISC représente l'ordinateur de jeu d'instructions réduit et

CISC représente l'ordinateur du jeu d'instructions complexes.

Architecture RISC (Reduced Instruction Set Computer)

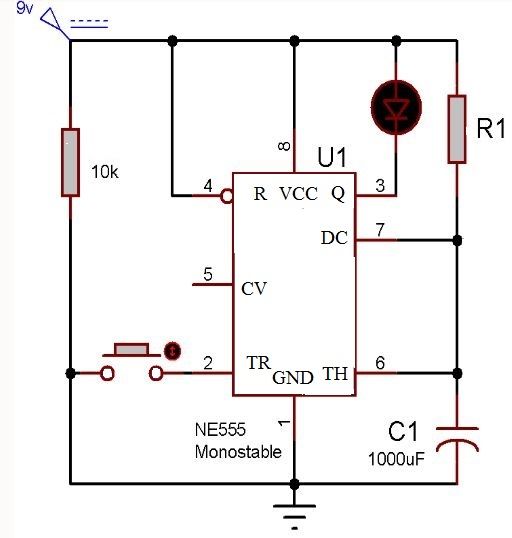

Architecture RISC

Le architecture de microcontrôleur qui utilise un ensemble d'instructions réduit et hautement optimisé est appelé ordinateur à jeu d'instructions réduit ou simplement appelé RISC. Il est également appelé architecture LOAD / STORE.

À la fin des années 1970 et au début des années 1980, les projets RISC ont été principalement développés à partir de Stanford, UC-Berkley et IBM. L'équipe de recherche John Coke d'IBM a développé RISC en réduisant le nombre d'instructions nécessaires pour traiter les calculs plus rapidement que le CISC. L'architecture RISC est plus rapide et les puces nécessaires à la fabrication de l'architecture RISC sont également moins chères que l'architecture CISC.

Caractéristiques typiques de l'architecture RISC

- La technique de pipelining de RISC, exécute plusieurs parties ou étapes d'instructions simultanément de sorte que chaque instruction sur le CPU est optimisée. Par conséquent, les processeurs RISC ont une horloge par instruction d'un cycle, et cela s'appelle une exécution en un cycle.

- Il optimise le utilisation du registre avec un plus grand nombre de registres dans le RISC et un plus grand nombre d'interactions dans la mémoire peuvent être évités.

- Des modes d'adressage simples, même des adressages complexes peuvent être effectués en utilisant l'arithmétique Opérations logiques ET / OU .

- Il simplifie la conception du compilateur en utilisant des registres à usage général identiques qui permettent à n'importe quel registre d'être utilisé dans n'importe quel contexte.

- Pour une utilisation efficace des registres et l'optimisation des utilisations de pipelining, un jeu d'instructions réduit est nécessaire.

- Le nombre de bits utilisés pour l'opcode est réduit.

- En général, il existe 32 registres ou plus dans le RISC.

Avantages de l'architecture de processeur RISC

- En raison du petit ensemble d'instructions de RISC, les compilateurs de langage de haut niveau peuvent produire du code plus efficace.

- RISC permet la liberté d'utiliser l'espace sur microprocesseurs en raison de sa simplicité.

- Au lieu d'utiliser Stack, de nombreux processeurs RISC utilisent les registres pour passer des arguments et contenir les variables locales.

- Les fonctions RISC n'utilisent que quelques paramètres et les processeurs RISC ne peuvent pas utiliser les instructions d'appel, et par conséquent, utilisent des instructions de longueur fixe qui sont faciles à canaliser.

- La vitesse de l'opération peut être maximisée et le temps d'exécution peut être minimisé.

- Il faut très peu de formats d'instructions (moins de quatre), quelques instructions (environ 150) et quelques modes d'adressage (moins de quatre).

Inconvénients de l'architecture du processeur RISC

- Avec l'augmentation de la longueur des instructions, la complexité augmente pour les processeurs RISC à exécuter en raison de son cycle de caractères par instruction.

- Les performances des processeurs RISC dépendent principalement du compilateur ou du programmeur car la connaissance du compilateur joue un rôle majeur lors de la conversion du code CISC en code RISC, par conséquent, la qualité du code généré dépend du compilateur.

- Tout en replanifiant le code CISC vers un code RISC, appelé extension de code, augmentera la taille. Et, la qualité de cette expansion de code dépendra encore une fois du compilateur, ainsi que du jeu d’instructions de la machine.

- Le cache de premier niveau des processeurs RISC est également un inconvénient du RISC, dans lequel ces processeurs ont de grandes caches mémoire sur la puce elle-même. Pour alimenter les instructions, ils nécessitent très systèmes de mémoire rapides .

Architecture CISC (Complex Instruction Set Computer)

L'intention principale de l'architecture de processeur CISC est d'accomplir la tâche en utilisant moins de lignes d'assemblage. À cette fin, le processeur est conçu pour exécuter une série d'opérations. L'instruction complexe est également appelée MULT, qui fonctionne banques de mémoire d'un ordinateur directement sans que le compilateur exécute des fonctions de stockage et de chargement.

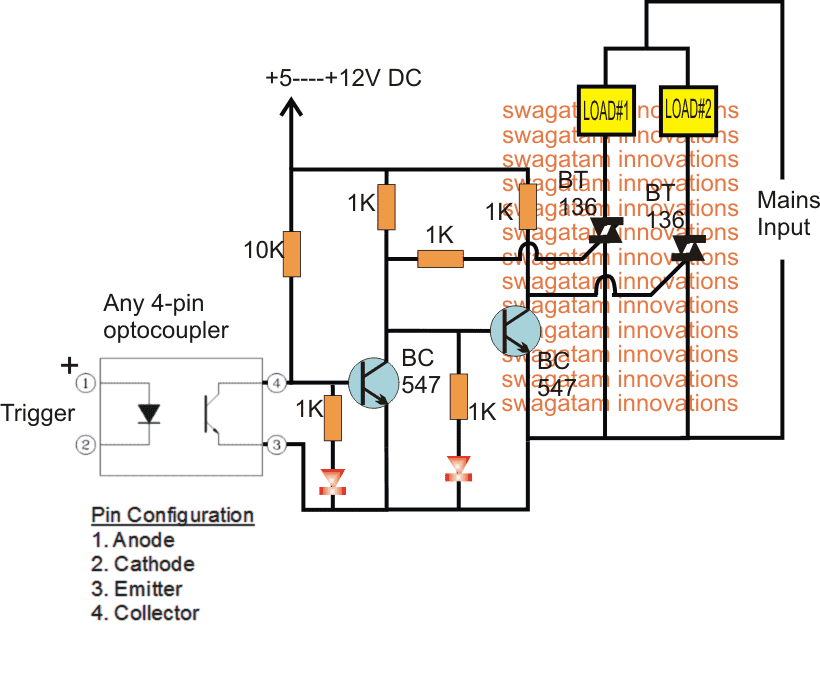

Architecture du SCRC

Caractéristiques de l'architecture CISC

- Pour simplifier l'architecture informatique, le CISC prend en charge la microprogrammation.

- Le CISC dispose d'un plus grand nombre d'instructions prédéfinies, ce qui facilite la conception et la mise en œuvre de langages de haut niveau.

- Le CISC comprend moins de registres et plus de modes d'adressage, généralement de 5 à 20.

- Le processeur CISC prend un temps de cycle variable pour l'exécution des instructions - cycles multi-horloges.

- En raison du jeu d'instructions complexe du CISC, la technique de pipelining est très difficile.

- Le SCRC comprend un plus grand nombre d'instructions, généralement de 100 à 250.

- Des instructions spéciales sont utilisées très rarement.

- Les opérandes en mémoire sont manipulés par des instructions.

Avantages de l'architecture CISC

- Chaque instruction de langage machine est regroupée en une instruction de microcode et exécutée en conséquence, puis est stockée intégrée dans la mémoire du processeur principal, appelée implémentation de microcode.

- Comme la mémoire du microcode est plus rapide que la mémoire principale, le jeu d'instructions du microcode peut être mis en œuvre sans réduction de vitesse considérable par rapport à une mise en œuvre câblée.

- L'ensemble du nouveau jeu d'instructions peut être géré en modifiant la conception du micro-programme.

- CISC, le nombre d'instructions nécessaires pour implémenter un programme peut être réduit en construisant des jeux d'instructions riches et peut également être amené à utiliser plus efficacement la mémoire principale lente.

- En raison du sur-ensemble d'instructions qui se compose de toutes les instructions précédentes, cela facilite le micro-codage.

Inconvénients de l'ICCA

- La durée d'horloge prise par différentes instructions sera différente - pour cette raison - les performances de la machine ralentissent.

- La complexité du jeu d'instructions et le matériel de la puce augmentent à mesure que chaque nouvelle version du processeur se compose d'un sous-ensemble de générations antérieures.

- Seulement 20% des instructions existantes sont utilisées dans un événement de programmation typique, même s'il existe de nombreuses instructions spécialisées qui ne sont même pas utilisées fréquemment.

- Les codes conditionnels sont définis par les instructions CISC comme un effet secondaire de chaque instruction qui prend du temps pour ce paramètre - et, comme l'instruction suivante change les bits de code de condition - le compilateur doit donc examiner les bits de code de condition avant que cela ne se produise.

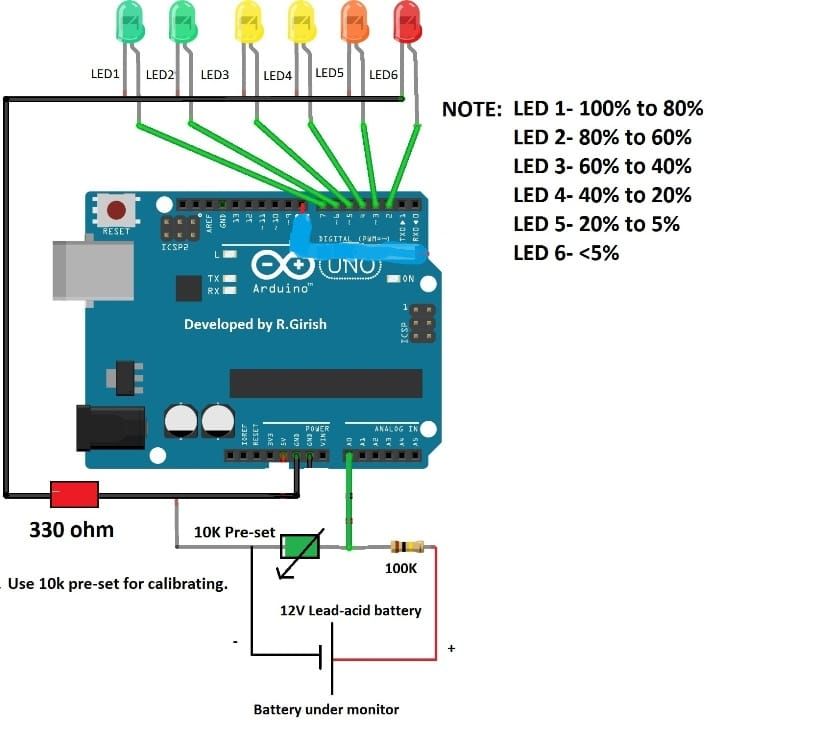

RISC contre. CISC

- Les cycles de gaspillage peuvent être évités par le programmeur en supprimant le code inutile dans le RISC, mais, tout en utilisant le code CISC conduit à des cycles de gaspillage en raison de l'inefficacité du CISC.

- Dans RISC, chaque instruction est destinée à effectuer une petite tâche de telle sorte que, pour effectuer une tâche complexe, plusieurs petites instructions soient utilisées ensemble, alors que seules quelques instructions sont nécessaires pour effectuer la même tâche en utilisant CISC - car il est capable d'exécuter une tâche complexe car les instructions sont similaires à un code en langage élevé.

- CISC est généralement utilisé pour les ordinateurs tandis que RISC est utilisé pour les téléphones intelligents, tablettes et autres appareils électroniques.

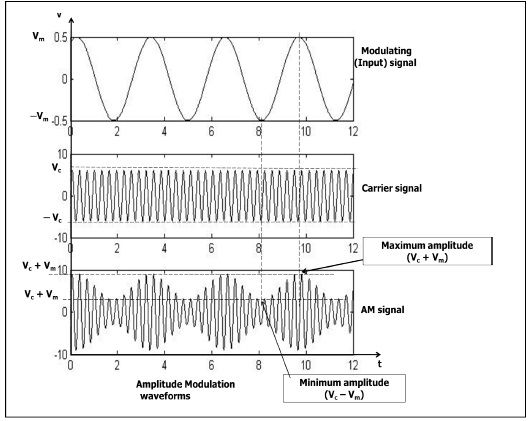

La figure suivante montre plus de différences entre RISC et CISC

RISC contre. CISC

Ainsi, cet article traite des caractéristiques des architectures RISC et CISC des avantages et des inconvénients de l'architecture des processeurs RISC et CISC de RISC et CISC, ainsi que des différences entre les architectures RISC et CISC avec une brève idée. Pour plus d'informations sur les architectures RISC et CISC, veuillez poster vos questions en commentant ci-dessous.

Crédits photo:

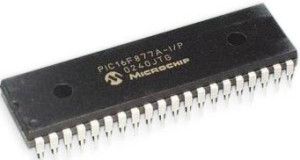

- Jeu d'instructions du processeur par arstechnica

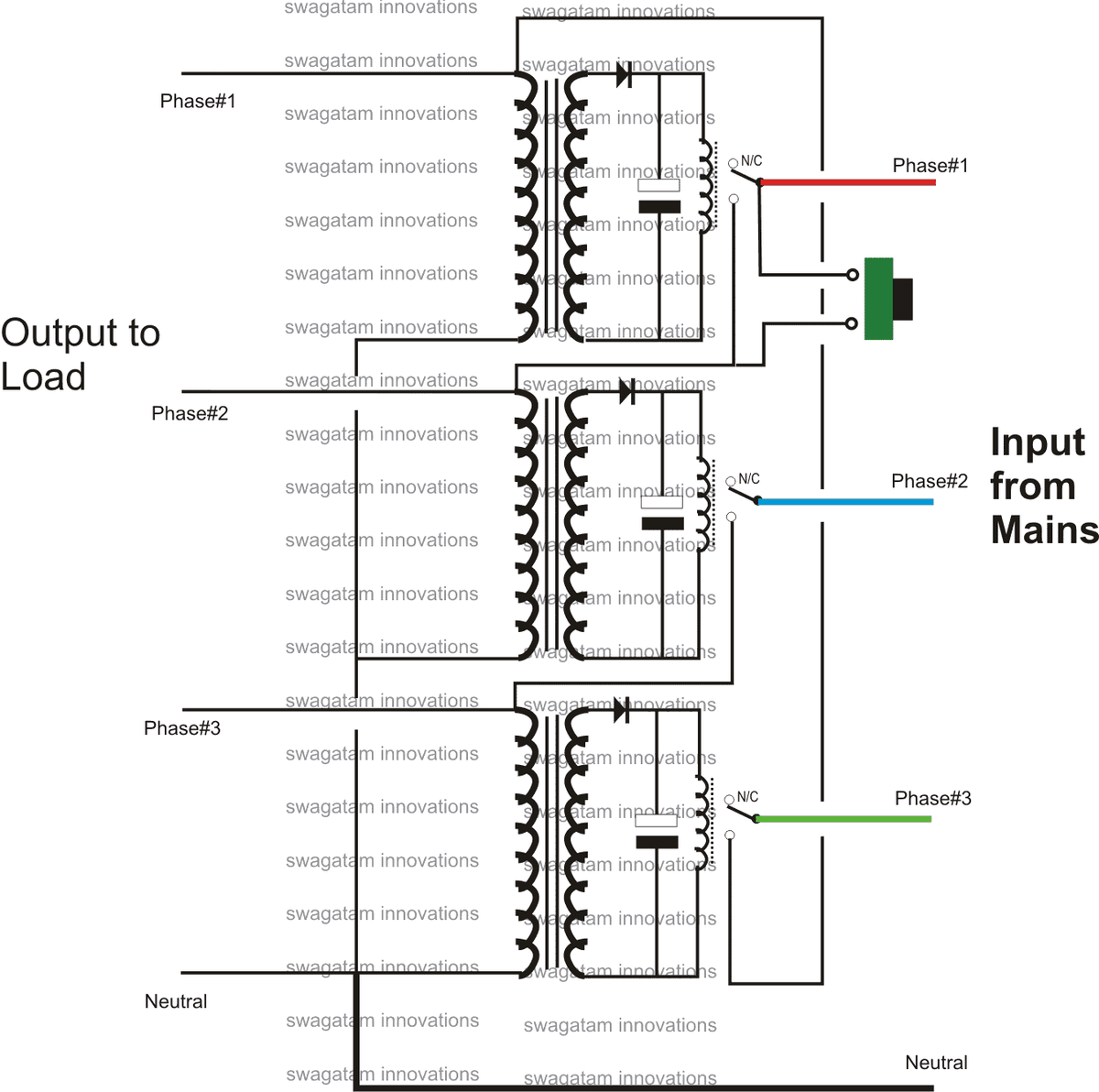

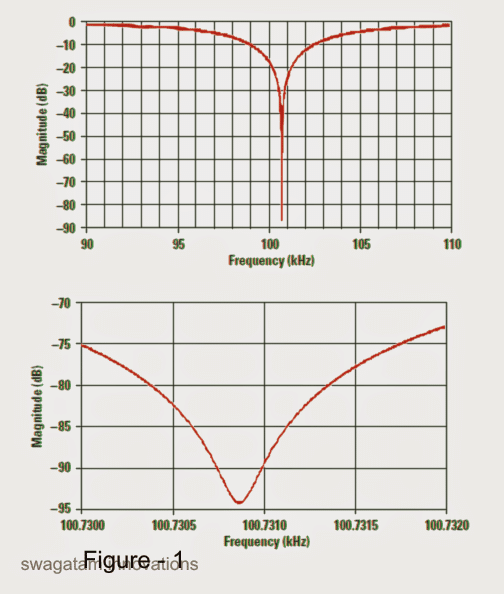

- Architecture RISC par concours lsi

- RISC vs CISC par csarassignation