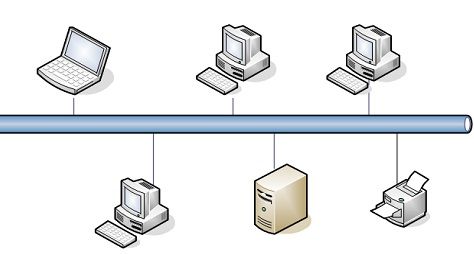

Pour l'exécution d'un programme informatique, il nécessite le fonctionnement synchrone de plus d'un composant d'un ordinateur. Par exemple, Processeurs - fournir les informations de contrôle nécessaires, les adresses… etc, les bus - pour transférer les informations et les données de et vers la mémoire vers les dispositifs d'E / S… etc. Le facteur intéressant du système serait la façon dont il gère le transfert d'informations entre les processeurs, la mémoire et les périphériques d'E / S. Habituellement, les processeurs contrôlent tout le processus de transfert des données, du lancement du transfert au stockage des données à la destination. Cela ajoute une charge sur le processeur et la plupart du temps, il reste dans l'état idéal, diminuant ainsi l'efficacité du système. Pour accélérer le transfert des données entre les périphériques d'E / S et la mémoire, le contrôleur DMA fait office de maître de station. Le contrôleur DMA transfère les données avec une intervention minimale du processeur.

Qu'est-ce qu'un contrôleur DMA?

Le terme DMA signifie accès direct à la mémoire. Le périphérique matériel utilisé pour l'accès direct à la mémoire est appelé le contrôleur DMA. DMA le contrôleur est une unité de contrôle , une partie du périphérique d'E / S circuit d'interface , qui peut transférer des blocs de données entre les périphériques d'E / S et la mémoire principale avec une intervention minimale du processeur.

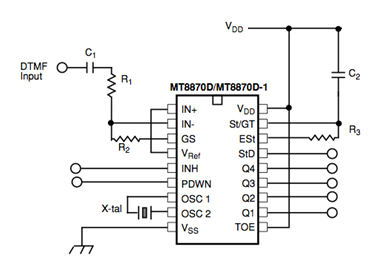

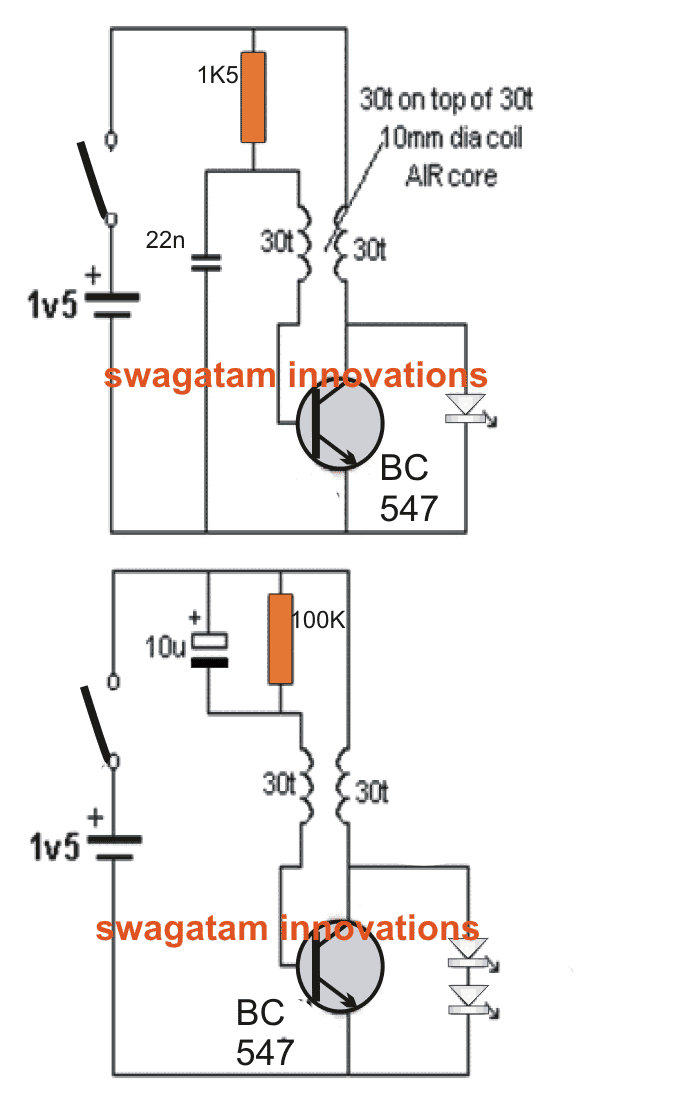

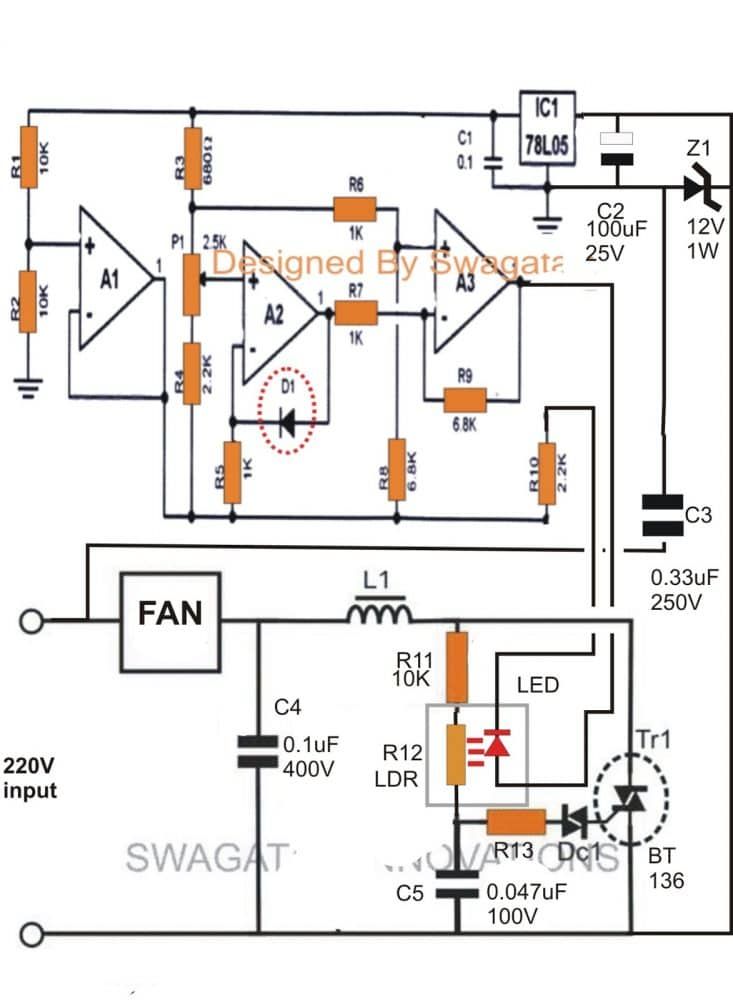

Diagramme de contrôleur DMA dans l'architecture informatique

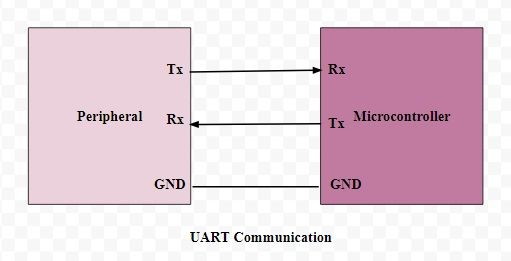

Le contrôleur DMA fournit une interface entre le bus et les périphériques d'entrée-sortie. Bien qu'il transfère les données sans intervention du processeur, il est contrôlé par le processeur. Le processeur lance le contrôleur DMA en envoyant l'adresse de départ, le nombre de mots dans le bloc de données et le sens de transfert des données. des périphériques d'E / S à la mémoire ou de la mémoire principale aux périphériques d'E / S. Plusieurs périphériques externes peuvent être connectés au contrôleur DMA.

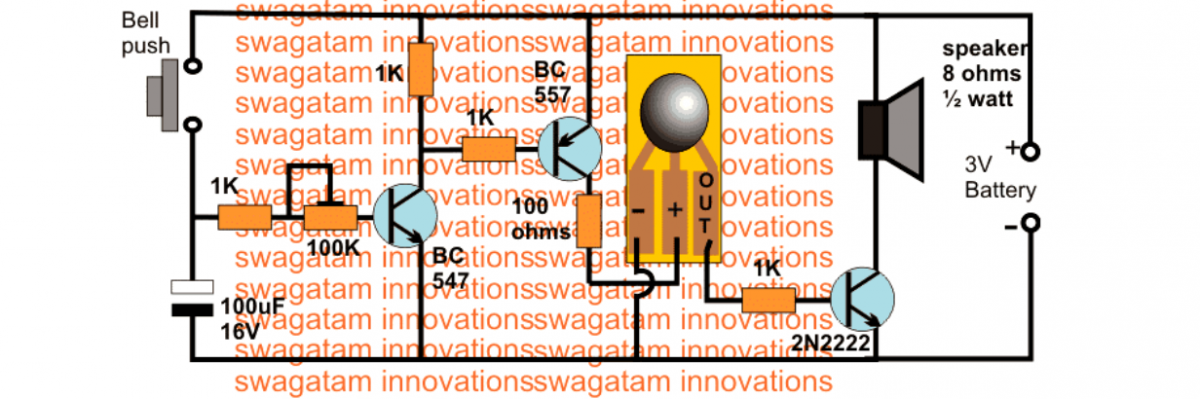

DMA en architecture informatique

Le contrôleur DMA contient une unité d'adresse, pour générer des adresses et sélectionner le périphérique d'E / S pour le transfert. Il contient également l'unité de contrôle et le décompte des données pour conserver les décomptes du nombre de blocs transférés et indiquer le sens de transfert des données. Lorsque le transfert est terminé, DMA informe le processeur en lançant une interruption. Le schéma fonctionnel typique du contrôleur DMA est illustré dans la figure ci-dessous.

Schéma fonctionnel typique du contrôleur DMA

Fonctionnement du contrôleur DMA

Le contrôleur DMA doit partager le bus avec le processeur pour effectuer le transfert de données. L'appareil qui maintient le bus à un instant donné est appelé maître de bus. Lorsqu'un transfert du périphérique d'E / S vers la mémoire ou vice verset doit être effectué, le processeur arrête l'exécution du programme en cours, incrémente le programme compteur, déplace les données sur la pile puis envoie un signal de sélection DMA au contrôleur DMA sur le bus d'adresse.

Si le contrôleur DMA est libre, il demande le contrôle du bus au processeur en augmentant le signal de demande de bus. Le processeur accorde le bus au contrôleur en augmentant le signal d'octroi de bus, maintenant le contrôleur DMA est le maître du bus. Le processeur lance le contrôleur DMA en envoyant les adresses mémoire, le nombre de blocs de données à transférer et la direction du transfert des données. Après avoir affecté la tâche de transfert de données au contrôleur DMA, au lieu d'attendre idéalement jusqu'à la fin du transfert de données, le processeur reprend l'exécution du programme après avoir récupéré les instructions de la pile.

Transfert de données dans l'ordinateur par le contrôleur DMA

Le contrôleur DMA a désormais le contrôle total des bus et peut interagir directement avec la mémoire et les périphériques d'E / S indépendamment du CPU. Il effectue le transfert de données selon les instructions de contrôle reçues par le processeur. Une fois le transfert de données terminé, il désactive le signal de demande de bus et la CPU désactive le signal d'accord de bus, déplaçant ainsi la commande des bus vers la CPU.

Lorsqu'un périphérique d'E / S souhaite initier le transfert, il envoie un signal de demande DMA au contrôleur DMA, pour lequel le contrôleur reconnaît s'il est libre. Ensuite, le contrôleur demande le processeur pour le bus, augmentant le signal de demande de bus. Après avoir reçu le signal d'autorisation de bus, il transfère les données de l'appareil. Pour un contrôleur DMA à n canaux, n nombre de périphériques externes peuvent être connectés.

Le DMA transfère les données selon trois modes, dont les suivants.

à) Mode rafale : Dans ce mode, le DMA ne transfère les bus à la CPU qu'après la fin du transfert de données complet. Pendant ce temps, si le CPU a besoin du bus, il doit rester idéal et attendre le transfert de données.

b) Mode de vol de cycle : Dans ce mode, DMA donne le contrôle des bus au CPU après le transfert de chaque octet. Il émet en permanence une demande de contrôle du bus, effectue le transfert d'un octet et renvoie le bus. Par ce processeur n'a pas besoin d'attendre longtemps s'il a besoin d'un bus pour une tâche de priorité plus élevée.

c) Mode transparent: Ici, DMA transfère les données uniquement lorsque la CPU exécute l'instruction qui ne nécessite pas l'utilisation de bus.

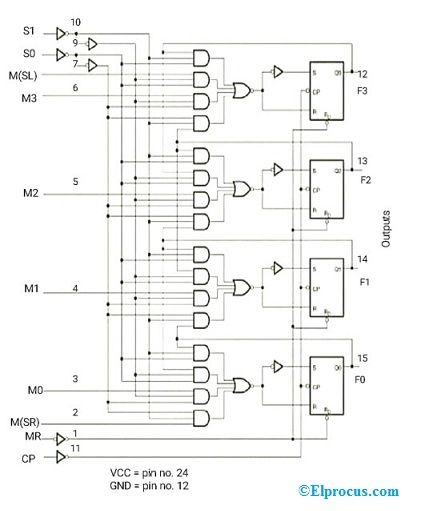

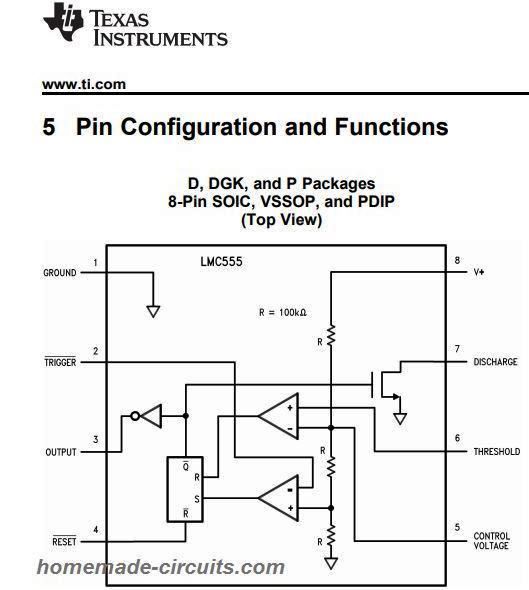

Contrôleur DMA 8237

- 8237 dispose de 4 canaux E / S avec la flexibilité d'augmenter le nombre de canaux.

- Chaque canal peut être programmé individuellement et dispose d'une adresse de 64k et d'une capacité de données.

- Le bloc de commande de synchronisation, le bloc de commande de commande de programme, le bloc d'encodeur prioritaire sont les trois blocs principaux du 8237A.

- La synchronisation interne et les signaux de commande externes sont pilotés par le bloc de commande de synchronisation.

- Diverses commandes données par le microprocesseur au DMA sont décodées par le bloc de commande de commande de programme.

- Le canal qui doit recevoir la priorité la plus élevée est déterminé par la priorité bloc codeur .

8237A a 27 registres internes.

8237A fonctionne en deux cycles: cycle idéal et cycle actif, où chaque cycle contient 7 états séparés composés d'une période d'horloge chacun.

S0- Le premier état, où le contrôleur a demandé le bus et attend l'acquittement du processeur.

S1, S2, S3, S4 sont appelés les états de fonctionnement du 8237A où le transfert réel des données a lieu. Si plus de temps est nécessaire pour les états d'attente de transfert, des SW sont ajoutés entre ces états.

Pour le transfert de mémoire à mémoire, des transferts de lecture à partir de la mémoire et d'écriture à la mémoire doivent être effectués. Huit états sont requis pour un transfert unique. Les quatre premiers états avec des indices S11, S12, S13, S14 effectuent le transfert de lecture depuis la mémoire et les quatre suivants S21, S22, S23, S24 sont pour le transfert d'écriture vers la mémoire.

Le DMA entre dans l'état idéal lorsqu'aucun canal ne demande de service et n'exécute l'état SI. SI est un état inactif où le DMA est inactif jusqu'à ce qu'il reçoive une demande. Dans cet état, le DMA est en condition de programme où le processeur peut programmer le DMA.

Lorsque DMA est dans l'état idéal et ne reçoit plus de demandes de canal, il émet un signal HRQ au processeur et entre dans l'état actif où il peut démarrer le transfert de données soit en mode rafale, en mode vol de cycle ou en mode transparent.

8237 Schéma des broches

Contrôleur DMA 8257

Lorsqu'il est associé à un périphérique à port d'E / S Intel 8212 unique, le contrôleur DMA 8257 forme un 4 canaux complet Contrôleur DMA . Dès réception d'une demande de transfert, le contrôleur 8257

- Acquiert le contrôle du bus système du processeur.

- Le périphérique connecté au canal de priorité la plus élevée est acquitté.

- Les bits les moins significatifs de l'adresse mémoire sont déplacés sur les lignes d'adresse A0-A7 du bus système.

- Le plus significatif 8 bits de l'adresse mémoire sont dirigés vers le port 8212 I / O via des lignes de données.

- Génère les signaux de commande appropriés pour le transfert de données entre les périphériques et les emplacements de mémoire adressés.

- Lorsque le nombre d'octets spécifié est transféré, le contrôleur informe la CPU de la fin du transfert en activant la sortie de comptage de bornes (TC).

Pour chaque canal, 8257 contient deux Registres 16 bits - 1) registre d'adresse DMA et 2) registre de comptage de terminal, qui doit être initialisé avant qu'un canal soit activé. L'adresse du premier emplacement mémoire à accéder est chargée dans le registre d'adresses DMA. Les 14 bits d'ordre inférieur de la valeur chargée dans le registre de comptage de terminal indiquent le nombre de cycles DMA moins un avant l'activation de la sortie de comptage de terminal. Le type d'opération pour un canal est indiqué par les deux bits les plus significatifs du registre de comptage de terminal.

8257 Schéma des broches

Avantages et inconvénients du contrôleur DMA

Les avantages et inconvénients du contrôleur DMA sont les suivants.

Avantages

- DMA accélère les opérations de mémoire en contournant l'implication du CPU.

- La surcharge de travail sur le processeur diminue.

- Pour chaque transfert, seuls quelques nombres de cycles d'horloge sont nécessaires

Désavantages

- Un problème de cohérence du cache peut être observé lorsque DMA est utilisé pour le transfert de données.

- Augmente le prix du système.

DMA ( Accès direct à la mémoire ) Le contrôleur est utilisé dans les cartes graphiques, les cartes réseau, les cartes son, etc. Le DMA est également utilisé pour le transfert intra-puce dans les processeurs multicœurs. Fonctionnant dans l'un de ses trois modes, le DMA peut réduire considérablement la charge du processeur. Dans lequel des modes de DMA avez-vous travaillé? Lequel des modes que vous considérez est le plus efficace?