Le transistor MOS est l'élément le plus fondamental dans la conception de circuits intégrés à grande échelle. Ces transistors sont généralement classés en deux types PMOS et NMOS. La combinaison de transistors NMOS et PMOS est connue sous le nom de Transistor CMOS . Le différent des portes logiques & autres dispositifs logiques numériques qui sont implémentés doivent avoir une logique PMOS. Cette technologie est peu coûteuse et a une bonne résistance aux interférences. Cet article traite de l'un des types de transistors MOS comme un transistor PMOS.

Qu'est-ce qu'un transistor PMOS ?

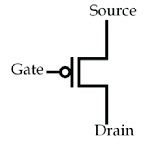

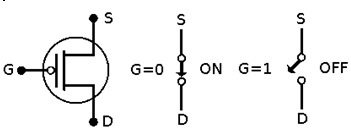

Le transistor PMOS ou semi-conducteur à oxyde métallique à canal P est un type de transistor dans lequel les dopants de type p sont utilisés dans la région du canal ou de la grille. Ce transistor est exactement l'inverse du transistor NMOS. Ces transistors ont trois bornes principales ; la source, la grille et le drain où la source du transistor est conçue avec un substrat de type p, et la borne de drain est conçue avec un substrat de type n. Dans ce transistor, les porteurs de charge comme les trous sont responsables de la conduction du courant. Les symboles du transistor PMOS sont illustrés ci-dessous.

Comment fonctionne le transistor PMOS ?

Le fonctionnement du transistor de type p est tout à fait opposé au transistor de type n. Ce transistor formera un circuit ouvert chaque fois qu'il obtiendra une tension non négligeable, ce qui signifie qu'il n'y a pas de flux d'électricité de la borne de grille (G) à la source (S). De même, ce transistor forme un circuit fermé lorsqu'il reçoit une tension d'environ 0 volt, ce qui signifie que le courant circule de la borne de grille (G) vers le drain (D).

Cette bulle est également connue sous le nom de bulle d'inversion. La fonction principale de ce cercle est donc d'inverser la valeur de la tension d'entrée. Si la borne de grille fournit une tension de 1, alors cet onduleur la changera en zéro et fera fonctionner le circuit en conséquence. Ainsi, la fonction du transistor PMOS et du transistor NMOS est tout à fait opposée. Une fois que nous les avons fusionnés en un seul circuit MOS, il deviendra alors un circuit CMOS (complémentaire métal-oxyde semi-conducteur).

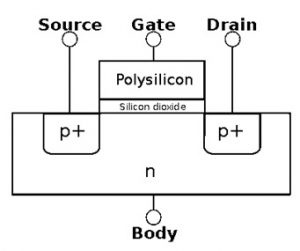

Coupe transversale du transistor PMOS

La section transversale du transistor PMOS est illustrée ci-dessous. Un transistor pMOS est construit avec un corps de type n comprenant deux régions semi-conductrices de type p qui sont adjacentes à la grille. Ce transistor a une grille de contrôle comme indiqué sur le schéma qui contrôle le flux d'électrons entre les deux bornes comme la source et le drain. Dans le transistor pMOS, le corps est maintenu à une tension +ve. Une fois que la borne de grille est positive, les bornes de source et de drain sont polarisées en inverse. Une fois que cela se produit, il n'y a plus de courant, donc le transistor sera éteint.

Une fois que la tension d'alimentation à la borne de grille est abaissée, les porteurs de charge positifs seront attirés vers le bas de l'interface Si-SiO2. Chaque fois que la tension devient suffisamment basse, le canal est inversé et crée une voie conductrice de la borne source au drain en permettant la circulation du courant.

Chaque fois que ces transistors traitent de la logique numérique, il y a généralement deux valeurs différentes comme 1 et 0 (ON et OFF). La tension positive du transistor est connue sous le nom de VDD qui représente la valeur logique haute (1) dans les circuits numériques. Les niveaux de tension VDD dans Logique TTL étaient généralement autour de 5V. À l'heure actuelle, les transistors ne peuvent pas réellement supporter des tensions aussi élevées car elles vont généralement de 1,5 V à 3,3 V. La basse tension est souvent appelée GND ou VSS. Ainsi, VSS signifie le « 0 » logique et il est également réglé normalement sur 0 V.

Circuit de transistors PMOS

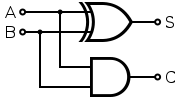

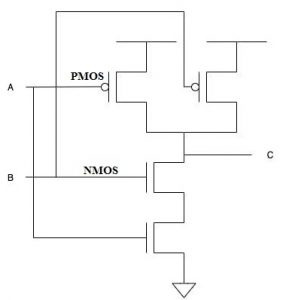

La conception de la porte NAND utilisant le transistor PMOS et le transistor NMOS est illustrée ci-dessous. Généralement, une porte NAND en électronique numérique est une porte logique également appelée porte NON-ET. La sortie de cette porte est au niveau bas (0) uniquement si les deux entrées sont au niveau haut (1) et sa sortie est complémentaire d'une porte ET. Si l'une des deux entrées est LOW (0), cela donne des résultats de sortie élevés.

Dans le circuit logique ci-dessous, si l'entrée A est 0 et B est 0, alors une entrée de pMOS produira '1' et une entrée de nMOS produira '0'. Ainsi, cette porte logique génère un '1' logique car elle est connectée à la source par un circuit fermé et détachée du GND par un circuit ouvert.

Lorsque A est « 0 » et B » est « 1 », alors une entrée de pMOS générera un « 1 » et une entrée de NMOS générera un « 0 ». Ainsi, cette porte produira un un logique car elle est reliée à la source par un circuit fermé et détachée du GND par un circuit ouvert. Lorsque A est '1' et B est '0', alors l'entrée 'B' de pMOS générera une sortie élevée (1) et l'entrée 'B' de NMOS générera une sortie aussi basse (0). Ainsi, cette porte logique générera un 1 logique car elle est connectée à la source via un circuit fermé et détachée du GND par un circuit ouvert.

Lorsque A est '1' et B est '1', alors une entrée de 'pMOS produira un zéro, et une entrée de nMOS générera '1'. Par conséquent, nous devons également vérifier l'entrée B de pMOS et nMOS. L'entrée B de pMOS générera un '0' et l'entrée B de nMOS générera un '1'. Ainsi, cette porte logique générera un '0' logique car elle est détachée de la source par un circuit ouvert et est connectée au GND via un circuit fermé.

Table de vérité

La table de vérité du circuit logique ci-dessus est donnée ci-dessous.

|

UNE |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

La tension de seuil du transistor PMOS est normalement le « Vgs » qui est nécessaire pour créer le canal appelé inversion de canal. Dans un transistor PMOS, le substrat et les bornes de source sont simplement connectés à 'Vdd'. Si nous commençons à réduire la tension par référence à la borne source à la borne de grille de Vdd à un point où vous remarquez l'inversion de canal, à cette position si vous analysez Vgs & source étant au potentiel élevé, vous obtiendrez une valeur négative. Ainsi, le transistor PMOS a une valeur Vth négative.

Processus de fabrication PMOS

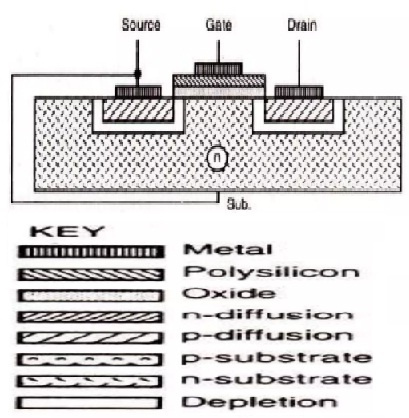

Les étapes impliquées dans la fabrication du transistor PMOS sont décrites ci-dessous.

Étape 1:

Une fine couche de plaquette de silicium est transformée en matériau de type N par simple dopage de matériau phosphoreux.

Étape 2:

Une couche épaisse de dioxyde de silicium (Sio2) est développée sur un substrat complet de type p.

Étape 3:

Maintenant, la surface est recouverte d'un photorésist sur l'épaisse couche de dioxyde de silicium.

Étape 4:

Après cela, cette couche est simplement exposée à la lumière UV à travers un masque qui définit les régions dans lesquelles la diffusion doit avoir lieu avec des canaux de transistor.

Étape 5 :

Ces régions sont gravées mutuellement avec le dioxyde de silicium sous-jacent de sorte que la surface de la plaquette est exposée à l'intérieur de la fenêtre définie par le masque.

Étape 6 :

La résine photosensible restante est détachée et une fine couche de Sio2 est développée généralement de 0,1 micromètre sur toute la surface de la puce. Après cela, du polysilicium est placé dessus pour former la structure de la grille. Une résine photosensible est placée sur toute la couche de polysilicium et expose la lumière UV à travers le masque2.

Étape 7 :

Les diffusions sont obtenues en chauffant la plaquette à la température maximale et en faisant passer le gaz avec les impuretés de type p souhaitées comme le bore.

Étape 8 :

Un dioxyde de silicium d'une épaisseur de 1 micromètre est développé et un matériau photorésistant est déposé dessus. Exposez la lumière ultraviolette avec le masque3 sur les zones préférées de la grille, de la source et du drain qui sont gravées pour effectuer les coupes de contact.

Étape 9 :

Maintenant, un métal ou de l'aluminium est déposé sur sa surface d'une épaisseur de 1 micromètre. Encore une fois, un matériau photorésistant est développé sur tout le métal et expose la lumière UV à travers le masque4 qui est gravé pour former la conception d'interconnexion requise. La structure finale du PMOS est illustrée ci-dessous.

Caractéristiques des transistors PMOS

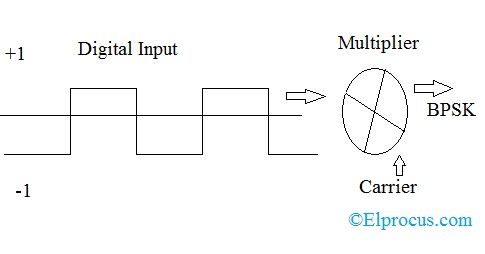

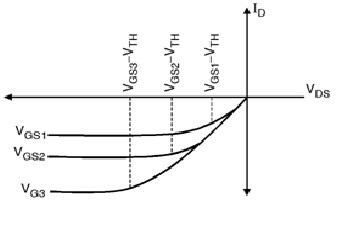

Les caractéristiques I-V du transistor PMOS sont présentées ci-dessous. Ces caractéristiques sont divisées en deux régions afin d'obtenir la relation entre le courant drain-source (I DS) ainsi que ses tensions aux bornes comme les régions linéaires et de saturation.

Dans une région de revêtement, l'IDS augmentera de manière linéaire lorsque le VDS (tension drain à source) augmentera, tandis que dans la région de saturation, l'IDS est stable et indépendant du VDS. La relation principale entre l'ISD (courant source-drain) et ses tensions aux bornes est dérivée par une procédure similaire du transistor NMOS. Dans ce cas, le seul changement sera que les porteurs de charge présents dans la couche d'inversion sont simplement des trous. Lorsque les trous se déplacent de la source au drain, le flux de courant est également le même.

Ainsi, le signe négatif apparaît dans l'équation actuelle. De plus, tous les biais appliqués aux bornes du dispositif sont négatifs. Ainsi, les caractéristiques ID - VDS du transistor PMOS sont indiquées ci-dessous.

L'équation du courant de drain pour le transistor PMOS dans la région linéaire est donnée par :

ID = – mp Cox

De même, l'équation du courant de drain pour le transistor PMOS dans la région de saturation est donnée par :

ID = – mp Cox (VSG – | V TH |p )^2

Où ‘mp’ est la mobilité du trou & ‘|VTH| p' est la tension de seuil du transistor PMOS.

Dans l'équation ci-dessus, le signe négatif indique que l'ID( courant de drain ) s'écoule du drain (D) vers la source (S) tandis que les trous s'écoulent dans le sens opposé. Lorsque la mobilité du trou est faible par rapport à la mobilité des électrons, les transistors PMOS souffrent de la capacité de la commande à faible courant.

Ainsi, il s'agit d'un aperçu du transistor PMOS ou du transistor mos de type p - fabrication, circuit et son fonctionnement. PMOS les transistors sont conçus avec une source p, un substrat n et un drain. Les porteurs de charge du PMOS sont des trous. Ce transistor conduit une fois qu'une basse tension est appliquée à la borne de grille. Les appareils basés sur PMOS sont moins sujets aux interférences que les appareils NMOS. Ces transistors peuvent être utilisés comme résistances commandées en tension, charges actives, miroirs de courant, amplificateurs trans-impédance, et également utilisés dans les commutateurs et les amplificateurs de tension. Voici une question pour vous, qu'est-ce qu'un transistor NMOS ?