Dans cet article, nous discutons des cotes d'avalanche du MOSFET et apprenons comment comprendre correctement cette cote dans la fiche technique, comment le paramètre est testé par le fabricant et les mesures pour protéger les MOSFET de ce phénomène.

Le paramètre avalanche aide non seulement à vérifier la robustesse des appareils, il aide également à filtrer les MOSFET les plus faibles ou ceux qui sont plus sensibles ou à risque de panne.

Qu'est-ce que l'indice d'avalanche MOSFET?

La cote d'avalanche du MOSFET est l'énergie maximale tolérable (millijoule) qu'un MOSFET peut supporter, lorsque sa tension drain-source dépasse la limite de tension de claquage maximale (BVDSS).

Ce phénomène se produit normalement dans les circuits de commutation MOSFET avec une charge inductive aux bornes de la borne de drain.

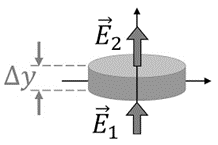

Pendant les périodes ON des cycles de commutation, l'inductance se charge, et pendant les périodes OFF, l'inductance libère son énergie stockée sous la forme de contre-électromotrice à travers la source-drain du MOSFET.

Cette tension inverse trouve son chemin à travers la diode du corps du MOSFET, et si sa valeur dépasse la limite maximale tolérable de l'appareil, provoque le développement d'une chaleur intense à l'intérieur de l'appareil, causant des dommages ou des dommages permanents à l'appareil.

Quand le MOSFET Avalanche a-t-il été introduit

Le paramètre Énergie avalanche et courant UIS (commutation inductive non bloquée) n'était en fait pas inclus dans les fiches techniques du MOSFET avant les années 1980.

Et c'est à ce moment-là qu'il a évolué non seulement pour devenir une spécification de fiche technique, mais aussi un paramètre que de nombreux consommateurs ont commencé à exiger que le FET soit testé avant de passer l'appareil à la production, en particulier si le MOSFET est conçu pour des implémentations d'alimentation ou de commutation.

Par conséquent, ce n'est qu'après les années 1980 que le paramètre d'avalanche a commencé à apparaître dans les fiches techniques, puis les techniciens de promotion ont commencé à comprendre que plus l'indice d'avalanche était élevé, plus l'appareil semblait être compétitif.

Les ingénieurs ont commencé à déterminer des techniques pour expérimenter le paramètre en ajustant quelques-unes de ses variables, qui ont été utilisées pour le processus de test.

De manière générale, plus l'énergie d'avalanche est grande, plus le MOSFET devient durable et solide. Par conséquent, un indice d'avalanche plus élevé représente des caractéristiques MOSFET plus fortes.

La plupart des fiches techniques FET auront normalement le paramètre d'avalanche inclus dans leur tableau des cotes maximales absolues, qui peut être trouvé directement sur la page d'entrée de la feuille de données. Surtout, vous pouvez voir les paramètres ici écrits comme courant d'avalanche et énergie d'avalanche, Eas.

Par conséquent, dans les fiches techniques MOSFET, l'énergie d'avalanche est présentée comme la quantité d'énergie que le MOSFET est capable de tolérer pendant qu'il est soumis au test d'avalanche, ou lorsque la tension de claquage maximale du MOSFET est franchie.

Courant d'avalanche et ISU

Cette tension de claquage maximale est déterminée par le test de courant d'avalanche, qui est réalisé par un test de commutation inductive non bridée ou le test UIS.

Par conséquent, lorsque les ingénieurs discutent du courant de l'ISU, ils peuvent faire référence au courant d'avalanche.

Un test de commutation inductive non bloquée est effectué pour déterminer le courant et donc l'énergie d'avalanche qui pourrait déclencher la défaillance du MOSFET.

Comme mentionné précédemment, ces grandeurs ou valeurs nominales dépendent énormément des spécifications de test, en particulier de la valeur d'inductance appliquée au moment du test.

Configuration du test

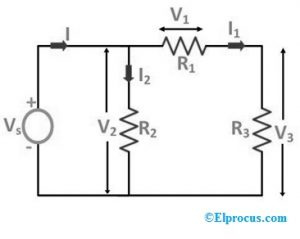

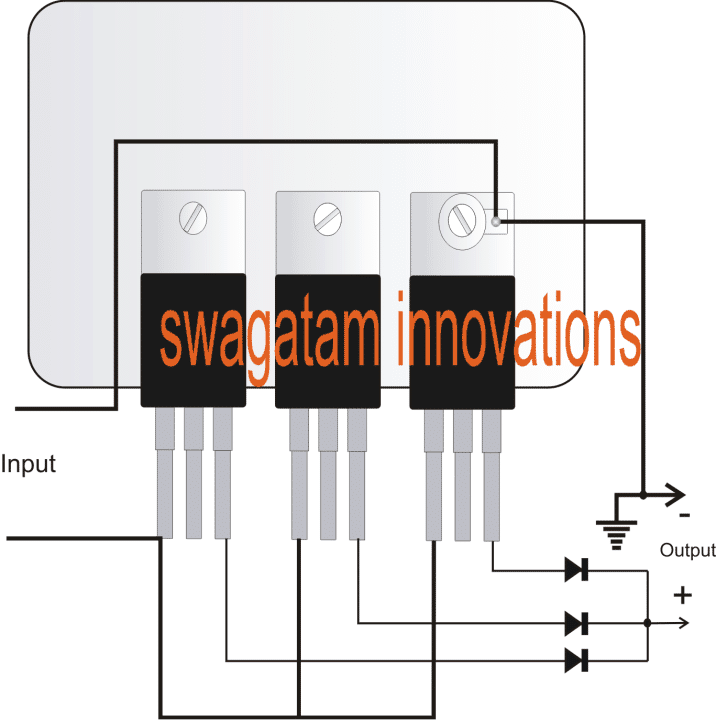

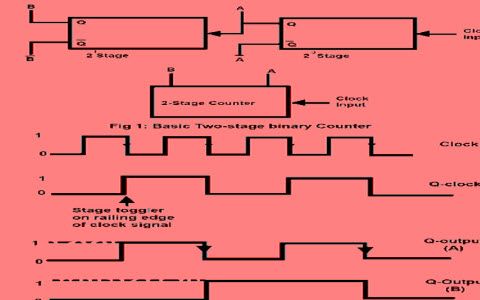

Le schéma suivant montre la configuration d'un circuit de test UIS standard.

Ainsi, nous voyons une alimentation en tension en série avec une inductance, L, qui est également en série avec le MOSFET sous test. On peut également voir un pilote de grille pour le FET dont la sortie est en série avec une résistance de grille R FET.

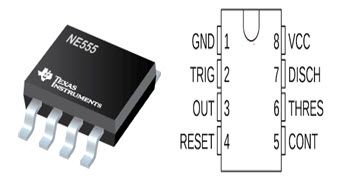

Dans l'image ci-dessous, nous trouvons le dispositif contrôleur LTC55140, qui est utilisé dans le laboratoire Texas Instrument pour évaluer les caractéristiques UIS du FET.

La caractéristique de l'ISU permet ensuite non seulement de connaître la cote de la fiche technique FET, mais également la valeur utilisée pour scanner le FET dans la procédure de test finale.

L'outil permet d'ajuster la valeur de l'inducteur de charge de 0,2 à 160 millihenries. Il permet le réglage de la tension de drain du MOSFET testé de 10 à 150 volts.

Ceci, en conséquence, permet de filtrer même les FET qui sont conçus pour ne supporter qu'une tension de claquage de 100 volts. Et, il devient possible d'appliquer des courants de drain de 0,1 à 200 ampères. Et c'est la gamme de courant de l'ISU que le FET peut avoir à tolérer pendant la procédure de test.

De plus, l'outil permet de définir différentes plages de températures du boîtier MOSFET, de -55 à +150 degrés.

Procédures de test

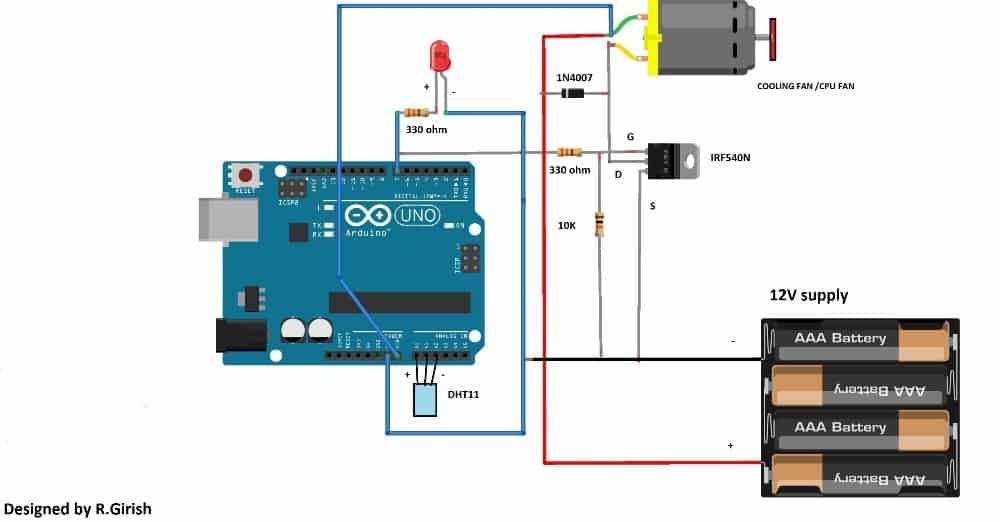

Le test UIS standard est implémenté en 4 étapes, comme illustré dans l'image suivante:

La première étape consiste en un test de pré-fuite, dans lequel la tension d'alimentation polarise le drain FET. Fondamentalement, l'idée ici est d'essayer de s'assurer que le FET fonctionne de la manière normale prévue.

Ainsi, dans la première étape, le FET est maintenu éteint. Il maintient la tension d'alimentation bloquée entre les bornes de l'émetteur-récepteur, sans subir aucune sorte de courant de fuite excessif qui le traverse.

Dans la deuxième étape, connue sous le nom de montée en puissance du courant d'avalanche, le FET est activé, ce qui fait chuter sa tension de drain. Il en résulte que le courant augmente progressivement à travers l'inducteur avec un di / dt constant. Donc, fondamentalement, à ce stade, l'inducteur est autorisé à se charger.

Dans la troisième étape, le test d'avalanche proprement dit est effectué, où le FET est pratiquement soumis à l'avalanche. Dans cette étape, le FET est désactivé en supprimant sa polarisation de grille. Cela se traduit par un di / dt massif traversant l'inducteur, provoquant une tension de drain FET dépassant la limite de tension de claquage du FET.

Cela oblige le FET à traverser la poussée d'avalanche. Dans ce processus, le FET absorbe toute l'énergie générée par l'inducteur et reste éteint, jusqu'à ce que la 4ème étape soit exécutée, impliquant le test de fuite après

Dans cette quatrième étape, le FET est à nouveau soumis à un test d'avalanche répété, juste pour être sûr que le MOSFET se comporte toujours normalement ou non. Si c'est le cas, alors le FET est réputé avoir réussi le test d'avalanche.

Ensuite, le FET doit passer plusieurs fois le test ci-dessus, dans lequel le niveau de tension de l'UIS est progressivement augmenté à chaque test, jusqu'au niveau où le MOSFET est incapable de résister et échoue au test de post-fuite. Et ce niveau de courant est noté comme étant la capacité maximale de résistance au courant UIS du MOSFET.

Calcul de l'énergie d'avalanche du MOSFET

Une fois que la capacité maximale de traitement du courant UIS du MOSFET est atteinte, à laquelle l'appareil tombe en panne, il devient beaucoup plus facile pour les ingénieurs d'estimer la quantité d'énergie dissipée à travers le FET pendant le processus d'avalanche.

En supposant que toute l'énergie stockée dans l'inducteur a été dissipée dans le MOSFET pendant l'avalanche, cette magnitude d'énergie peut être déterminée à l'aide de la formule suivante:

ESTCOMME= 1 / 2L x IDEdeux

ESTCOMMEnous donne la grandeur de l'énergie stockée à l'intérieur de l'inductance, qui est égale à 50% de la valeur d'inductance multipliée par le courant au carré, traversant l'inductance.

De plus, on a observé que lorsque la valeur de l'inducteur augmentait, la quantité de courant qui était responsable de la panne du MOSFET diminuait en fait.

Cependant, cette augmentation de la taille de l'inducteur compense en fait cette réduction de courant dans la formule d'énergie ci-dessus d'une manière que la valeur d'énergie augmente littéralement.

Énergie d'avalanche ou courant d'avalanche?

Ce sont les deux paramètres, qui peuvent semer la confusion chez les consommateurs, tout en vérifiant une fiche technique MOSFET pour le taux d'avalanche.

Copyright © Texas Instruments Incorporated

De nombreux fabricants de MOSFET testent intentionnellement le MOSFET avec des inducteurs plus grands, afin qu'ils puissent se vanter d'une plus grande amplitude d'énergie d'avalanche, donnant l'impression que le MOSFET est testé pour résister à d'énormes énergies d'avalanche, et a donc une durabilité accrue aux avalanches.

Mais la méthode ci-dessus d'utilisation d'un inducteur plus grand semble trompeuse, c'est exactement pourquoi les ingénieurs de Texas Instruments testent avec une inductance plus petite de l'ordre de 0,1 mH, de sorte que le MOSFET testé soit soumis à un courant d'avalanche plus élevé et à des niveaux de stress de rupture extrêmes.

Ainsi, dans les fiches techniques, ce n'est pas l'énergie d'avalanche, mais plutôt le courant d'avalanche qui devrait être plus important en quantité, qui affiche une meilleure robustesse du MOSFET.

Cela rend le test final très rigoureux et permet de filtrer autant de MOSFET plus faibles que possible.

Cette valeur de test n'est pas seulement utilisée comme valeur finale avant que la mise en page FET ne soit transmise pour la production, mais c'est également la valeur qui est entrée dans la feuille de données.

Dans l'étape suivante, la valeur de test ci-dessus est déclassée de 65%, de sorte que l'utilisateur final puisse obtenir une marge de tolérance plus large pour ses MOSFET.

Ainsi, par exemple, si le courant d'avalanche testé était de 125 ampères, la valeur finale qui est entrée dans la fiche technique se trouve être de 81 ampères, après le déclassement.

Courant d'avalanche du MOSFET par rapport au temps passé dans l'avalanche

Un autre paramètre associé au MOSFET de puissance et mentionné dans les fiches techniques, en particulier pour les MOSFET conçus pour les applications de commutation, est la capacité de courant d'avalanche en fonction du temps passé en avalanche. Ce paramètre est normalement indiqué par rapport à la température du boîtier du MOSFET à 25 degrés. Pendant le test, la température du boîtier est augmentée à 125 degrés.

Dans cette situation, la température du boîtier du MOSFET du MOSFET est très proche de la température de jonction réelle de la puce en silicium du MOSFET.

Dans cette procédure, lorsque la température de jonction de l'appareil augmente, vous pouvez vous attendre à voir une certaine dégradation, ce qui est tout à fait normal? Cependant, si le résultat montre un niveau élevé de dégradation, cela peut indiquer les signes d'un dispositif MOSFET intrinsèquement faible.

Par conséquent, du point de vue de la conception, on essaie de s'assurer que la dégradation ne dépasse pas 30% pour une augmentation de la température du boîtier de 25 à 125 degrés.

Comment protéger le MOSFET du courant d'avalanche

Comme nous l'avons appris des discussions ci-dessus, l'avalanche dans les MOSFET est développée en raison de la commutation électromagnétique inductive à haute tension à travers la diode du corps du MOSFET.

Si cette tension contre-électromotrice dépasse la valeur nominale maximale de la diode du corps, provoque une génération de chaleur extrême dans l'appareil et des dommages ultérieurs.

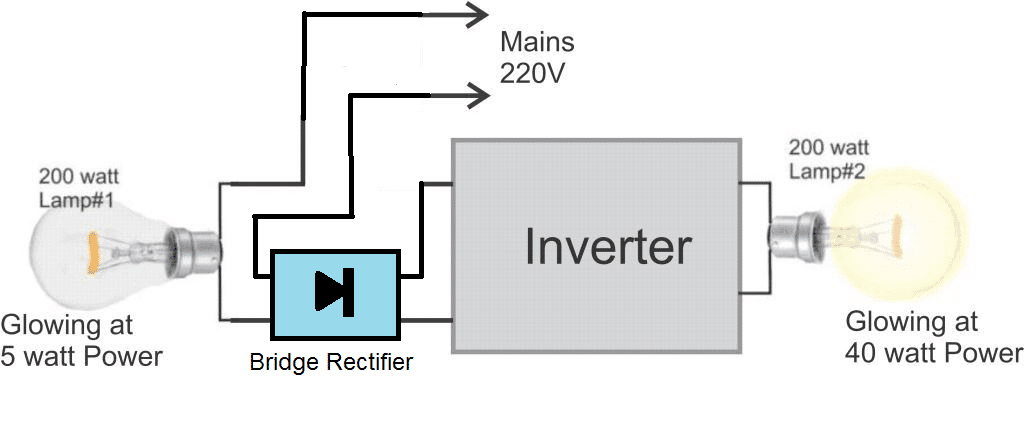

Cela implique que si la tension inductive EMF est autorisée à passer à travers une diode de dérivation externe appropriée, à travers le drain-émetteur du FET peut aider à éviter le phénomène d'avalanche.

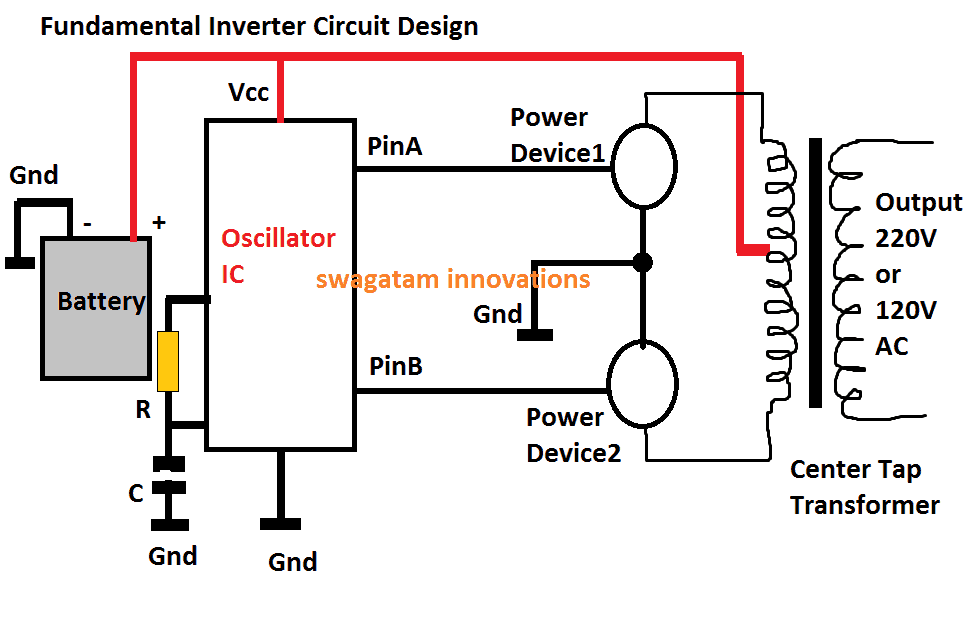

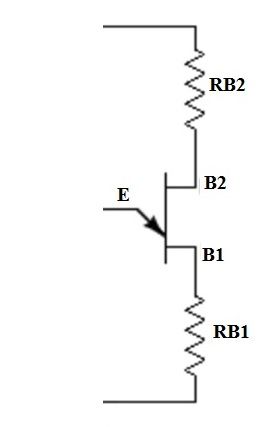

Le schéma suivant suggère la conception standard de l'ajout d'une diode drain-émetteur externe pour renforcer la diode de corps interne du MOSFET.

Courtoisie: Avalanche du MOSFET

Une paire de: Conversion d'allumage à étincelle gaspillée en étincelle séquentielle, pour une combustion à haut rendement Un article: Circuit UPS en ligne simple