Le processus de conception du matériel numérique s'est considérablement transformé au cours des dernières années. Ainsi, de petits circuits numériques peuvent être mis en œuvre en utilisant des PAL et des PLA. Chaque appareil est utilisé pour mettre en œuvre divers circuits qui n'ont pas besoin de plus que le nombre de i / ps, o / ps et les conditions du produit qui sont offerts dans la puce spécifique. Ces puces sont inadaptées à des tailles assez modestes, supportant normalement un nombre mutuel d'entrées et de sorties ne dépassant pas 32. Pour la conception de ces circuits qui nécessitent plus d'entrées et de sorties, soit de nombreux PLA / PAL peuvent être utilisés, soit un type plus classe de puce peut être utilisé appelé CPLD (dispositif logique programmable complexe). Une puce CPLD comprend plusieurs blocs de circuits sur une seule puce avec des ressources de câblage internes pour attacher les blocs de circuits. Chaque bloc de circuit est comparable à un PLA ou un PAL.

Qu'est-ce qu'un périphérique logique programmable complexe?

L'acronyme du CPLD est «Composants logiques programmables complexes», c'est un type de circuit intégré que les concepteurs d'applications conçoivent pour implémenter du matériel numérique comme les téléphones mobiles. Ceux-ci peuvent gérer des conceptions sciemment plus élevées que les SPLD (simples dispositifs logiques programmables), mais offrent moins de logique que les FPGA ( matrices de portes programmables sur site Les CPLD comprennent de nombreux blocs logiques, chacun des blocs comprend 8 à 16 macrocellules. Comme chaque bloc logique exécute une fonction spécifique, toutes les macrocellules d'un bloc logique sont entièrement connectées. Selon l'utilisation, ces blocs peuvent ou non être connectés les uns aux autres.

Dispositif logique programmable complexe

La plupart des CPLD (dispositifs logiques programmables complexes) ont des macrocellules avec une somme de fonction logique et une option FF (bascule) . En fonction de la puce, la fonction de logique combinatoire prend en charge de 4 à 16 termes de produit avec fan-in inclus. Les CPLD diffèrent également en termes de registres à décalage et de portes logiques. Pour cette raison, les CPLD avec un grand nombre de portes logiques peuvent être utilisés à la place des FPGA. Une autre spécification CPLD signifie le nombre de termes de produit qu'une macrocellule peut accomplir. Les termes du produit sont le produit de signaux numériques qui exécutent une fonction logique spécifique.

Les CPLD sont disponibles sous plusieurs formes de packages IC et familles logiques. Les CPLD diffèrent également en termes de tension d'alimentation, de courant de fonctionnement, de courant de veille et de dissipation de puissance. De plus, ceux-ci peuvent être obtenus avec diverses quantités de mémoire et divers types de support de mémoire. Habituellement, la mémoire est exprimée en bits / mégabits. La prise en charge de la mémoire comprend la ROM, la RAM et la RAM à double port. Il comprend également une mémoire CAM (mémoire adressable par contenu) ainsi qu'une mémoire FIFO (premier entré, premier sorti) et une mémoire LIFO (dernier entré, dernier sorti).

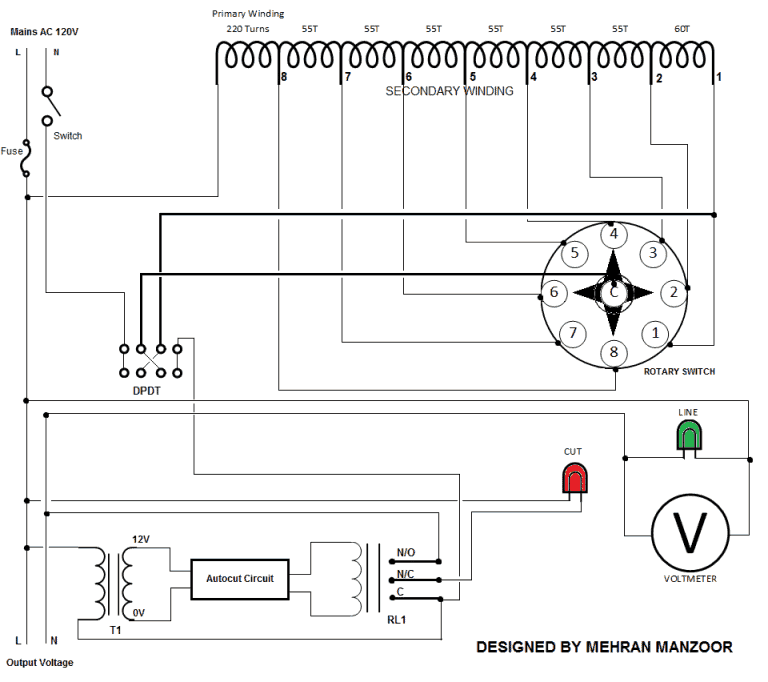

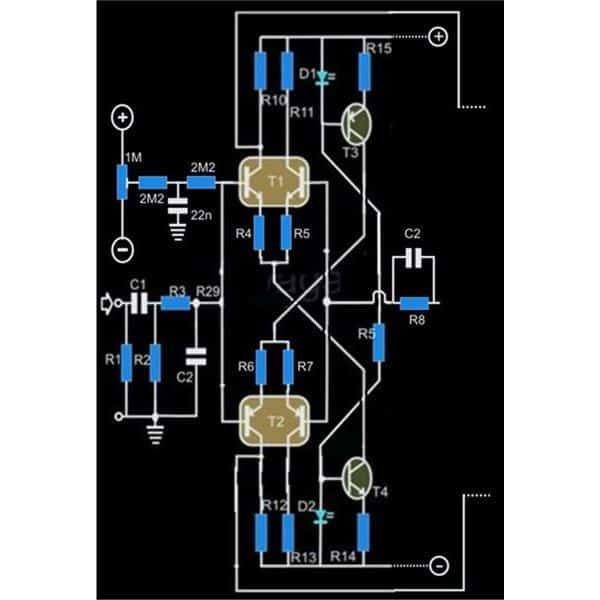

Architecture d'un dispositif logique programmable complexe

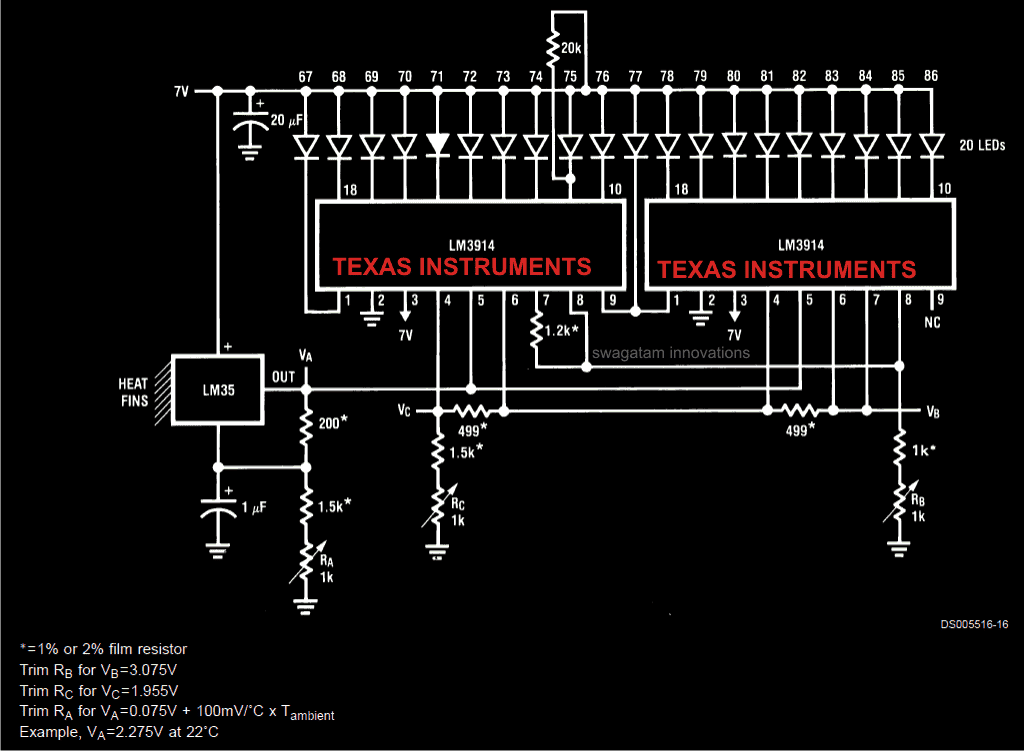

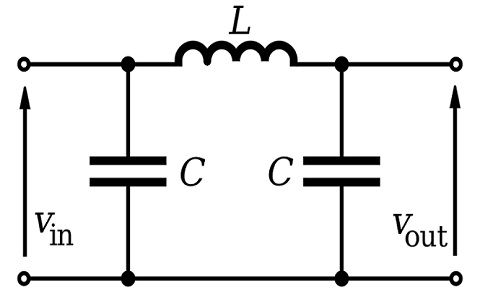

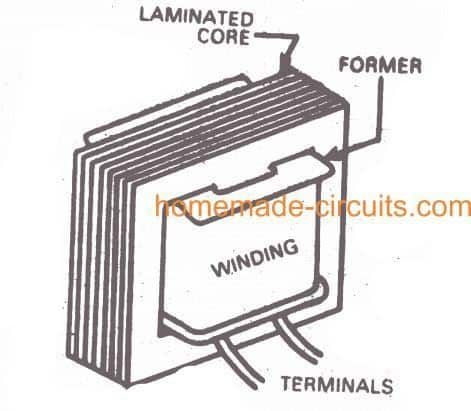

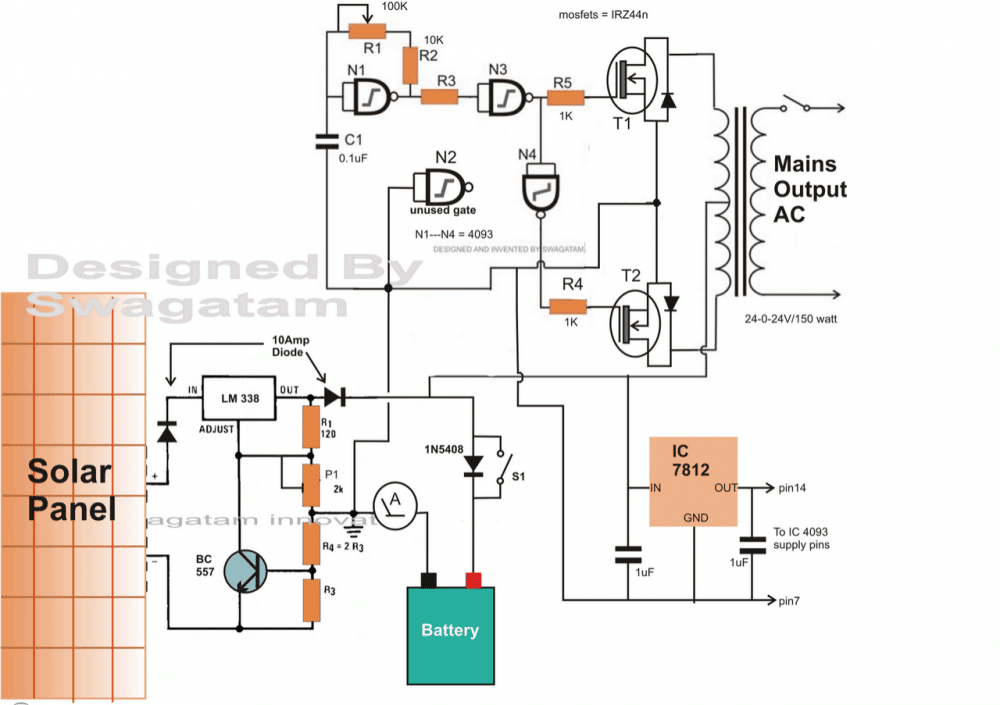

Un dispositif logique programmable complexe comprend un groupe de FB programmables (blocs fonctionnels). Les entrées et sorties de ces blocs fonctionnels sont reliées entre elles par une GIM (matrice d'interconnexion globale). Cette matrice d'interconnexion est reconfigurable, afin de pouvoir modifier les contacts entre les blocs fonctionnels. Il y aura des blocs d'entrée et de sortie qui nous permettront d'unir CPLD au monde extérieur. L'architecture du CPLD est illustrée ci-dessous.

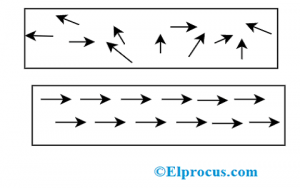

Généralement, le FB programmable ressemble au tableau de portes logiques , où un tableau de portes ET peut être programmé et les portes OU sont stables. Mais, chaque fabricant a sa façon de penser pour concevoir le bloc fonctionnel. Un o / p répertorié peut être trouvé en actionnant les signaux de retour obtenus à partir des sorties de la porte OU.

Architecture CPLD

Dans la programmation CPLD, la conception est d'abord codée en langage Verilog ou VHDL une fois que le code est (simulé et synthétisé. Pendant la synthèse, le modèle CPLD (appareil cible) est sélectionné à la main et une liste de réseaux de cartographie basée sur la technologie est produite. Cette liste peut être fermée -adaptation à l'architecture CPLD authentique en utilisant un processus de lieu et de route, généralement réalisé par le logiciel de localisation et de route du propriétaire de CPLD Company. Ensuite, l'opérateur effectuera des processus de confirmation. Si tout va bien, il utilisera le CPLD, sinon il le réorganisera.

Problèmes d'architecture du CPLD

Lors de l'examen d'un dispositif logique programmable complexe à utiliser dans la conception, certains problèmes d'architecture suivants peuvent être pris en compte

- La technologie de programmation

- La capacité du bloc fonctionnel

- La capacité d'E / S

Certaines familles de CPLD de différents détaillants comprennent

- Familles Altera MAX 7000 et MAX 9000

- Familles Atmel ATF et ATV

- Famille LSI ISP Lattice

- Famille MACH Lattice (Vantis)

- Famille Xilinx XC9500

Familles de CPLD

Applications du CPLD

Les candidatures des CPLD comprennent les éléments suivants

- Les dispositifs logiques programmables complexes sont idéaux pour les applications de contrôle critiques hautes performances.

- CPLD peut être utilisé dans les conceptions numériques pour exécuter les fonctions de chargeur de démarrage

- CPLD est utilisé pour charger les données de configuration d'un réseau de portes programmable sur site à partir d'une mémoire non volatile.

- Généralement, ceux-ci sont utilisés dans les petites applications de conception comme le décodage d'adresse

- Les CPLD sont fréquemment utilisés dans de nombreuses applications, comme dans les appareils portables à piles et sensibles aux coûts en raison de leur faible taille et de leur faible consommation d'énergie.

Il s'agit donc d'une architecture complexe de dispositifs logiques programmables et de ses applications. Nous espérons que vous avez une meilleure compréhension de ce concept. De plus, toute question concernant ce concept ou pour mettre en œuvre tous projets électriques et électroniques , veuillez donner vos précieuses suggestions en commentant dans la section des commentaires ci-dessous. Voici une question pour vous, quelle est la différence entre CPLD et FPGA?

Crédits photo:

- CPLD wikimedia

- Architecture du CPLD slidesharecdn