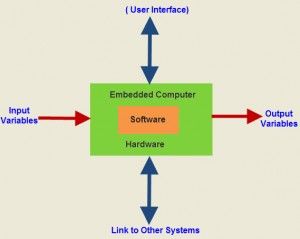

L'ECL (logique couplée à l'émetteur) a été inventée pour la première fois chez IBM en août 1956 par Hannon S. Yourke. Cette logique est également connue sous le nom de logique de mode courant, utilisée dans les ordinateurs IBM 7090 et 7094. La famille ECL est très rapide par rapport à logique numérique familles. Généralement, cette famille logique offre un délai de propagation inférieur à 1 ns. Il s'agit d'une famille logique basée sur des transistors à jonction bipolaire. C'est le circuit de la famille logique le plus rapide accessible pour concevoir un système logique conventionnel. Cet article donne un aperçu d'un circuit logique couplé à l'émetteur , travaillant avec des applications.

Qu'est-ce que la logique couplée à l'émetteur ?

La logique couplée à l'émetteur est la meilleure BJT -famille logique basée sur la logique utilisée dans la conception de systèmes logiques conventionnels. Parfois, on l'appelle aussi logique en mode courant qui est une technologie numérique à très haut débit. Généralement, ECL est considéré comme le circuit intégré logique le plus rapide où il réalise son fonctionnement à grande vitesse en utilisant une très petite variation de tension et en évitant également que les transistors n'entrent dans la région de saturation.

Une mise en œuvre d'ECL utilise une tension d'alimentation positive connue sous le nom de PECL ou ECL à référence positive. Dans les premières portes ECL, une alimentation en tension négative est utilisée en raison de l'immunité au bruit. Après cela, ECL à référence positive est devenu très célèbre en raison de ses niveaux logiques plus compatibles par rapport aux familles logiques TTL.

La logique couplée à l'émetteur dissipe une énorme quantité de puissance statique, cependant, sa consommation globale de courant est faible par rapport à CMOS à hautes fréquences. Ainsi, ECL est principalement bénéfique dans les circuits de distribution d'horloge et les applications à haute fréquence.

Caractéristiques de la logique couplée à l'émetteur

Les fonctionnalités d'ECL les rendront utilisés dans de nombreuses applications hautes performances.

- ECL fournit deux sorties qui sont toujours complémentaires car le fonctionnement du circuit est basé sur un amplificateur différentiel.

- Cette famille logique est principalement adaptée aux procédés de fabrication monolithique car les niveaux logiques sont fonction des rapports de résistance.

- Les appareils de la famille ECL génèrent la sortie juste et complémentaire de la fonction proposée sans utiliser d'onduleurs extérieurs. Par conséquent, cela diminue le nombre de paquets et les besoins en énergie et diminue également les problèmes liés aux retards.

- Les dispositifs ECL dans la conception d'amplificateurs différentiels offrent une grande flexibilité de performances, de sorte que les circuits ECL permettent d'être utilisés à la fois comme circuits numériques et linéaires.

- La conception de la porte ECL a une impédance d'entrée normalement élevée et faible, ce qui est extrêmement propice à l'obtention d'une grande diffusion ainsi qu'à une capacité d'entraînement.

- Les dispositifs ECL génèrent une consommation de courant constante sur l'alimentation pour simplifier la conception de l'alimentation.

- Les dispositifs d'ECL comprenant des sorties d'émetteur ouvertes leur permettent simplement d'inclure une capacité de commande de ligne de transmission.

Circuit logique couplé à l'émetteur

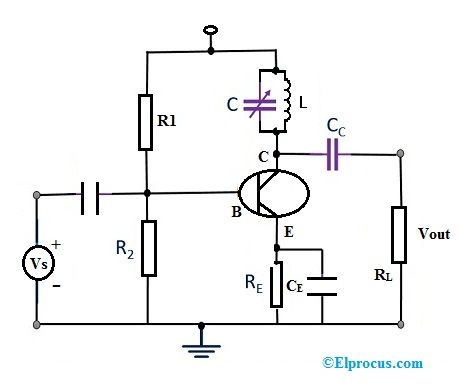

Le circuit logique couplé à l'émetteur pour l'onduleur est illustré ci-dessous, conçu avec des résistances et des transistors. Dans ce circuit, les bornes d'émetteur de deux transistors sont simplement reliées à la résistance de limitation de courant RE qui sert à éviter que le transistor n'entre en saturation. Ici, la sortie du transistor est prise à partir de la borne du collecteur au lieu de la borne de l'émetteur. Ce circuit fournit deux sorties Vout (sortie inverseuse) et Vout2 (sortie non inverseuse) et la borne d'entrée comme Vin où une entrée haute ou basse est donnée. +Vcc = 5V.

Comment fonctionne la logique couplée à l'émetteur ?

Le fonctionnement de la logique couplée à l'émetteur est que chaque fois que l'entrée HIGH est donnée au circuit ECL, le transistor 'Q1' s'allume et le transistor Q2 s'éteint, mais le transistor Q1 n'est pas saturé. Cela tirera donc la sortie VOUT2 vers HIGH et la valeur de la sortie VOUT1 sera LOW en raison de la chute dans R1.

De même, lorsque la valeur VIN donnée à ECL est LOW, cela rendra le transistor Q1 OFF et le transistor Q2 ON. Ainsi, le transistor Q2 n'entrera pas en saturation. Ainsi, la sortie VOUT1 sera tirée à la valeur HIGH et la valeur de sortie VOUT2 sera faible en raison de la chute de la résistance R2.

Voyons comment les transistors Q1 et Q2 s'allument et s'éteignent lorsqu'une tension est appliquée.

Les deux transistors comme Q1 et Q2 dans ce circuit sont connectés en tant qu'amplificateur différentiel par une résistance d'émetteur commune.

Les alimentations en tension pour cet exemple de circuit sont VCC = 5,0, VBB = 4,0 et VEE = 0 V. Les valeurs d'entrée de niveau HAUT et BAS sont simplement définies comme étant de 4,4 V et 3,6 V. En fait, ce circuit génère des niveaux de sortie BAS et HAUT qui sont supérieurs de 0,6 volt ; cependant, cela est corrigé dans les circuits ECL réels.

Une fois que Vin est HIGH, le transistor Q1 est activé, mais pas saturé et le transistor Q2 est désactivé. Ainsi, la tension de sortie comme VOUT2 est tirée à 5 V à travers la résistance R2 et on peut montrer que la chute de tension à travers la résistance R1 est d'environ 0,8 V de sorte que VOUT1 = 4,2 V (LOW). De plus VE = VOUT1 – VQ1 => 4,2V – 0,4V = 3,8V car le transistor Q1 est complètement activé.

Une fois que Vin est BAS, le transistor Q2 sera allumé, mais pas saturé et le transistor Q1 sera éteint. Par conséquent, VOUT1 est tiré à 5,0 V à l'aide d'une résistance R1 et on peut montrer que VOUT2 est de 4,2 V. Aussi VE => VOUT2 - VQ2 => 4,2V - 0,8V => 3,4V lorsque le transistor Q2 est activé.

En ECL, les deux transistors ne sont jamais en saturation car t Les variations de tension d'entrée/sortie sont assez petites comme 0,8 V et l'impédance d'entrée est élevée et la résistance de sortie est faible. Cela permet à ECL de fonctionner plus rapidement avec un délai de propagation réduit.

Circuit de porte logique OU / NOR couplé à un émetteur à deux entrées

Le circuit de porte logique OU / NOR couplé à un émetteur à deux entrées est illustré ci-dessous. Ce circuit est conçu en modifiant le circuit inverseur ci-dessus. La modification consiste à ajouter un transistor supplémentaire du côté entrée.

Le fonctionnement de ce circuit est très simple. Lorsque les entrées appliquées aux transistors Q1 et Q2 sont basses, la sortie 1 (Vout1) passe à une valeur HAUTE. Donc, ce Vout1 correspond à la sortie de la porte NOR.

Simultanément, si le transistor Q3 est activé, il rendra la deuxième sortie (Vout2) HAUTE. Ainsi, cette sortie Vou2 correspond à la sortie de la porte OU.

De la même manière, si les deux entrées des transistors Q1 et Q2 sont HAUTES, il activera les transistors Q1 et Q2 et fournira la sortie basse à la borne VOUT1.

Si le transistor Q3 est désactivé tout au long de cette opération, il fournira une sortie élevée à la borne VOUT2. Ainsi, la table de vérité pour la porte OR/NOR est donnée ci-dessous.

|

Contributions |

Contributions | OU |

NI |

|

UN |

B | Oui | Oui |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Caractéristiques de la logique couplée à l'émetteur

Les caractéristiques d'ECL sont les suivantes.

- Par rapport à TTL, ECL a un temps de propagation plus rapide allant de 0,5 à 2 ns. Mais, la dissipation de puissance logique couplée à l'émetteur est plus élevée que TTL, comme 30 mW.

- Les tensions d'E/S d'ECL ont une petite oscillation comme 0,8.

- L'impédance d'entrée d'ECL est élevée et la résistance de sortie est faible ; par conséquent, le transistor change d'état très rapidement.

- La capacité de sortance des ECL est élevée et les retards de porte sont faibles.

- La logique o/p d'ECL passe d'un état BAS à un état ÉLEVÉ, mais les niveaux de tension pour ces états varient entre TTL et EC.

- L'immunité au bruit de l'ECL est de 0,4 V.

Avantages et inconvénients

La avantages de la logique couplée à l'émetteur sont discutés ci-dessous.

- La sortance d'ECL est de 25, ce qui est meilleur que TTL et faible par rapport à CMOS.

- Le temps de propagation moyen d'ECL est de 1 à 4 ns, ce qui est meilleur que CMOS et

- TTL. Ainsi, on l'appelle la famille logique la plus rapide.

- Lorsque les BJT en émetteur couplés des portes logiques travaillent dans la région active, alors ils ont la vitesse maximale par rapport à toutes les familles logiques.

- Les portes ECL génèrent des sorties complémentaires.

- Les pics de commutation de courant ne sont pas là dans les câbles d'alimentation.

- Les sorties peuvent être couplées conjointement pour fournir la fonction OU câblé.

- Les paramètres d'ECL ne changent pas beaucoup avec la température.

- Le non. de fonctions accessibles depuis une seule puce est élevé.

La inconvénients de la logique couplée à l'émetteur sont discutés ci-dessous.

- Il a une marge de bruit extrêmement réduite, c'est-à-dire ± 200 mV.

- La dissipation de puissance est élevée par rapport aux autres portes logiques.

- Pour s'interfacer avec d'autres familles logiques, des décalages de niveau sont nécessaires.

- La sortance limite la charge capacitive.

- Comparé à Durée de vie , les portes ECL sont chères.

- Par rapport à CMOS et TTL, l'immunité au bruit ECL est la pire.

Applications

Les applications de la logique couplée à l'émetteur comprennent les suivantes.

- La logique couplée à l'émetteur est utilisée comme technologie logique et d'interface dans les dispositifs de communication à très haut débit comme les interfaces d'émetteur-récepteur à fibre optique, les réseaux Ethernet et ATM (mode de transfert asynchrone).

- ECL est une famille logique basée sur BJT où son fonctionnement à grande vitesse peut être obtenu en utilisant une variation de tension relativement faible et en évitant que les transistors ne se déplacent dans la région de saturation.

- ECL est utilisé dans la fabrication des circuits ASLT au sein de l'IBM 360/91.

- ECL évite l'utilisation de transistors empilés en utilisant une entrée/sortie de polarisation asymétrique et une rétroaction positive entre les transistors primaires et secondaires pour obtenir une fonction d'inverseur.

- L'ECL est utilisé dans l'électronique extrêmement rapide.

Ainsi, ceci est un aperçu d'une logique couplée à l'émetteur ou ECL - circuit, fonctionnement, fonctionnalités, caractéristiques et applications. ECL est la famille logique la plus rapide basée sur BJT par rapport aux autres familles logiques numériques. Il atteint sa vitesse de fonctionnement maximale en utilisant une petite variation de tension et en évitant que les transistors ne se déplacent dans la région de saturation. Cette famille logique fournit un délai de propagation incroyable de 1ns et dans les dernières familles ECL, ce délai est diminué. Voici une question pour vous, quel est un autre nom pour ECL ?