Les deux principaux types de FET qui existent actuellement sont: JFET et MOSFET.

Les MOSFET peuvent être classés en type d'appauvrissement et type d'amélioration. Ces deux types définissent le mode de fonctionnement fondamental des MOSFET, tandis que le terme MOSFET lui-même est l'abréviation de transistor à effet de champ métal-oxyde-semiconducteur.

Étant donné que les deux types ont des caractéristiques de fonctionnement différentes, nous les évaluerons séparément dans différents articles.

Différence entre le MOSFET d'amélioration et de déplétion

Fondamentalement, contrairement aux MOSFET d'amélioration, les MOSFET à appauvrissement sont dans un état passant même en présence d'un 0 V aux bornes des terminaux porte-source (VGS).

Pour un MOSFET d'amélioration, la tension grille-source (VGS) doit être supérieure à sa tension de seuil grille-source (VGS (th)) afin de le faire conduire .

Cependant, pour un MOSFET à appauvrissement à canal N, sa valeur VGS (th) est supérieure à 0 V. Cela signifie que même si VGS = 0 V, un MOSFET à appauvrissement est capable de conduire le courant. Pour le désactiver, le VGS d'un MOSFET d'appauvrissement doit être réduit en dessous du VGS (th) (négatif).

Dans ce présent article, nous discuterons du type d'appauvrissement MOSFET, qui aurait des caractéristiques correspondant à celles d'un JFET. La similitude est entre la coupure et la saturation près de IDSS.

Construction de base

La figure 5.23 montre la structure interne de base d'un MOSFET de type à épuisement à canal n.

Nous pouvons trouver un bloc de matériau de type p créé à partir d'une base de silicium. Ce bloc s'appelle le substrat.

Le substrat est la base ou la fondation sur laquelle un MOSFET est construit. Pour certains MOSFET, il est lié en interne au terminal «source». De plus, de nombreux appareils offrent une sortie supplémentaire sous la forme de SS, avec un MOSFET à 4 bornes, comme le montre la figure 5.23.

Le drain et les bornes de source sont connectés par des contacts conducteurs à des emplacements dopés n, et reliés par un canal n, comme indiqué sur la même figure.

La grille est également reliée à une couche métallique, bien qu'elle soit isolée du canal n par une fine couche de dioxyde de silicium (SiOdeux).

SiOdeuxpossède une forme unique de propriété d'isolation appelée diélectrique qui crée un champ électrique opposé en lui-même en réponse à un champ électrique appliqué de l'extérieur.

Étant une couche isolante, le matériau SiOdeuxnous offre les informations importantes suivantes:

Une isolation complète est développée entre la borne de porte et le canal mosfet avec ce matériau.

De plus, c'est à cause de SiOdeux, la porte du mosfet est capable de présenter un degré d'impédance d'entrée extrêmement élevé.

En raison de cette propriété d'impédance d'entrée élevée vitale, le courant de grille Igest pratiquement zéro ampère pour toute configuration MOSFET polarisée en courant continu.

Fonctionnement et caractéristiques de base

Comme on peut le voir sur la figure 5.24, la tension grille-source a été configurée à zéro volt en connectant les deux bornes ensemble, tandis qu'une tension VDSest appliqué aux bornes de drain et de source.

Avec le réglage ci-dessus, le côté drain établit un potentiel positif par les électrons libres du canal n, avec un courant équivalent à travers le canal JFET. En outre, le courant résultant VGS= 0V est toujours identifié comme IDSS, comme indiqué sur la figure 5.25

Nous pouvons voir que sur la figure 5.26 la tension de source de grille VGSreçoit un potentiel négatif sous la forme de -1V.

Ce potentiel négatif tente de forcer les électrons vers le substrat du canal p (puisque les charges se repoussent) et de tirer des trous du substrat du canal p (puisque les charges opposées s'attirent).

Selon l'ampleur de ce biais négatif VGSc'est-à-dire qu'une recombinaison des trous et des électrons a lieu qui se traduit par la réduction des électrons libres dans le canal n disponible pour la conduction. Des niveaux plus élevés de biais négatif entraînent un taux de recombinaison plus élevé.

Le courant de drain est par conséquent réduit à mesure que la condition de polarisation négative ci-dessus augmente, ce qui est prouvé sur la figure 5.25 pourGSniveaux de VGS= -1, -2 et ainsi de suite, jusqu'à la marque de pincement de -6V.

Le courant de drain qui en résulte avec le tracé de la courbe de transfert se déroule comme celui d'un JFET.

Maintenant, pour le V positifGSvaleurs, la grille positive attirera les électrons en excès (porteurs libres) du substrat de type p, en raison du courant de fuite inverse. Cela établira de nouveaux porteurs par le biais de collisions résultantes à travers les particules en accélération.

Comme la tension grille-source a tendance à augmenter à la vitesse positive, le courant de drain montre une augmentation rapide, comme le montre la figure 5.25 pour les mêmes raisons que celles décrites ci-dessus.

L'écart développé entre les courbes de VGS= 0V et VGS= +1 montre distinctement la quantité par laquelle le courant a augmenté en raison de la variation 1 - V du VGS

En raison de l'augmentation rapide du courant de drain, nous devons faire attention au courant nominal maximal, sinon il pourrait franchir la limite de tension de grille positive.

Par exemple, pour le type d'appareil représenté sur la figure 5.25, l'application d'un VGS= + 4V entraînerait une augmentation du courant de drain à 22,2 mA, ce qui pourrait dépasser la limite maximale de claquage (courant) de l'appareil.

La condition ci-dessus montre que l'utilisation d'une tension grille-source positive génère un effet amélioré sur la quantité de porteuses libres dans le canal, par opposition à lorsque VGS= 0V.

C'est pourquoi la région de tension de grille positive sur les caractéristiques de drain ou de transfert est généralement connue sous le nom de région d'amélioration . Cette région se situe entre la coupure et le niveau de saturation de IDSSou la région d'épuisement.

Résolution d'un problème d'exemple

Avantages et applications

Contrairement aux MOSFET en mode amélioration, où nous constatons que le courant de drain chute à zéro en réponse à une tension de grille à source nulle, le FET en mode d'appauvrissement moderne présente un courant perceptible avec une tension de grille nulle. Pour être précis, la résistance drain-source est généralement de 100 Ohms en tension nulle.

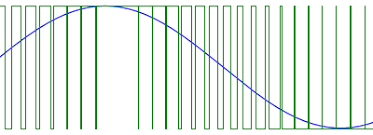

Comme indiqué dans le graphique ci-dessus, les rds de résistance ON(sur)vs la plage de signaux analogiques ressemble à une réponse pratiquement plate. Cette caractéristique, en conjonction avec les niveaux de faible capacité de ces dispositifs de type à épuisement avancé, leur permet d'être spécifiquement idéaux comme commutateurs analogiques pour les applications de commutation audio et vidéo.

L'attribut «normalement activé» du MOSFET en mode d'appauvrissement permet au dispositif d'être parfaitement adapté aux régulateurs de courant FET uniques.

Un tel exemple de circuit peut être vu dans la figure suivante.

La valeur Rs peut être déterminée à l'aide de la formule:

Rs= VGSdésactivé[1 - (jeré/JEDSS)1/2] / JEré

où jeré est la quantité de courant régulé nécessaire à la sortie.

Le principal avantage des MOSFET en mode d'appauvrissement dans les applications de source de courant est leur capacité de drain minimale, ce qui les rend appropriés pour les applications de polarisation dans les circuits à faible fuite d'entrée et à vitesse moyenne (> 50 V / us).

La figure ci-dessous présente un frontal différentiel à faible courant de fuite d'entrée utilisant un double FET à fonction de faible fuite.

D'une manière générale, chaque côté du JFET sera biaisé à ID = 500 uA. Par conséquent, le courant pouvant être obtenu pour la compensation de charge et les capacités parasites devient limité à 2ID ou, dans des cas comme celui-ci, à 1,0 mA. Les caractéristiques correspondantes du JFET sont prouvées en production et garanties sur la fiche technique.

Cs symbolise la capacité de sortie de la source de courant «queue» de l'étage d'entrée. Cette capacité est cruciale dans les amplificateurs non inverseurs, en raison du fait que l'étage d'entrée subit des échanges de signaux importants dans tout ce réseau et que les courants de charge en Cs pourraient être importants. Dans le cas où des sources de courant normales sont utilisées, cette capacité de queue pourrait être responsable de la détérioration notable de la vitesse de balayage dans les circuits non inverseurs (par rapport aux applications inverseuses, où les courants de charge en Cs ont tendance à être minimes).

La baisse de la vitesse de balayage pourrait être exprimée comme suit:

1 / 1+ (Cs / Sc)

Tant que Cs est inférieur à Cc (le condensateur de compensation), il peut y avoir pratiquement aucune variation de la vitesse de balayage. En travaillant avec le DMOS FET, Cs peut être d'environ 2 pF. Cette stratégie produit une énorme amélioration de la vitesse de montée. Lorsque des déficits de courant supérieurs à 1 à 5 mA sont nécessaires, l'appareil peut être polarisé en mode d'amélioration pour générer jusqu'à 20 mA pour un VGS maximum de +2,5 V, avec une capacité de sortie minimale continuant d'être un aspect clé.

L'application suivante ci-dessous présente un circuit de source de courant en mode d'amélioration approprié.

Un interrupteur analogique `` normalement allumé '' pourrait être construit pour les besoins où une condition standard devient nécessaire pendant une panne de tension d'alimentation, par exemple dans la gamme automatique d'outils de test ou pour assurer un démarrage précis des circuits logiques à la mise en marche.

La tension de seuil négative réduite de l'appareil offre des prérequis de base pour le variateur et permet de travailler avec une tension minimale.

Le circuit ci-dessous montre les facteurs de polarisation communs pour tout commutateur analogique DMOS en mode d'épuisement.

Pour provoquer l'arrêt de l'appareil, une tension négative devient nécessaire sur le portail. Cela dit, la résistance à l'état passant pourrait être minimisée lorsque le FET est en outre amélioré en utilisant une tension de grille positive, ce qui le permet spécifiquement dans la région de mode d'amélioration avec la région de mode de déplétion.

Cette réponse peut être observée dans le graphique suivant.

Le gain haute fréquence de l'unité, associé à ses faibles valeurs de capacité, offre une «valeur de mérite» accrue. C'est vraiment un élément crucial dans l'amplification VHF et UHF, qui spécifie le produit gain-bande passante (GBW) du FET, qui pourrait être décrit comme:

GBW = gfs / 2 Pi (Cdans+ Cen dehors)

MOSFET de type à déplétion à canal p

La construction d'un MOSFET de type à appauvrissement à canal p est l'inverse parfait d'une version à canal n représentée sur la figure 5.23. Cela signifie que le substrat prend maintenant la forme d'un type n et le canal devient un type p, comme on peut le voir sur la figure 5.28a ci-dessous.

L'identification des bornes reste inchangée, mais la tension et les polarités de courant sont inversées, comme indiqué sur la même figure. Les caractéristiques du drain seraient exactement celles illustrées sur la figure 5.25, sauf VDSsigne qui dans ce cas aura une valeur négative.

Le courant de drain Irémontre une polarité positive dans ce cas aussi, c'est parce que nous avons déjà inversé sa direction. VGSmontre une polarité opposée, ce qui est compréhensible, comme indiqué sur la figure 5.28c.

Parce que VGSest inversé produit une image miroir pour les caractéristiques de transfert comme indiqué sur les figures 5, 28b.

Cela signifie que le courant de drain augmente dans le V positifGSrégion à partir du point de coupure à VGS= Vp jusqu'à ce que jeDSS, puis il continue d'augmenter à mesure que la valeur négative de VGSmonte.

Symboles

Les signes graphiques d'un MOSFET de type à épuisement des canaux n et p peuvent être observés dans la figure 5.29 ci-dessus.

Observez la manière dont les symboles sélectionnés visent à représenter la véritable structure de l'appareil.

L'absence d'interconnexion directe (du fait de l'isolation de la grille) entre la grille et le canal est symbolisée par un écart entre la grille et les différentes bornes du symbole.

La ligne verticale qui représente le canal est fixée entre le drain et la source et est «maintenue» par le substrat.

Deux groupes de symboles sont fournis dans la figure ci-dessus pour chaque type de canal pour mettre en évidence le fait que dans certains dispositifs, le substrat peut être accessible de l'extérieur tandis que dans d'autres, cela peut ne pas être vu.

MOSFET (type d'amélioration)

Bien que les MOSFET de type d'appauvrissement et de type d'amélioration se ressemblent avec leurs structures internes et leur mode fonctionnel, leurs caractéristiques peuvent être très différentes.

La principale différence est le courant de drain qui dépend d'un niveau spécifique de tension grille-source pour l'action de coupure.

Précisément, un MOSFET de type à amélioration de canal n peut fonctionner avec une tension grille / source positive, au lieu d'une plage de potentiels négatifs qui peuvent normalement avoir un impact sur un MOSFET de type à épuisement.

Construction de base

Vous pouvez visualiser le MOSFET de type d'amélioration de canal n dans les

Fig. 5.31.

Une section de matériau de type p est créée à travers une base de silicium et, comme appris avant, elle est appelée substrat.

Ce substrat est parfois attaché en interne avec la broche source dans un MOSFET de type à déplétion, tandis que dans certains cas, il se termine comme un quatrième conducteur pour permettre un contrôle externe de son niveau de potentiel.

Les bornes de source et de drain sont comme d'habitude jointes à l'aide de contacts métalliques à des régions dopées n.

Cependant, il peut être important de visualiser que sur la figure 5.31 le canal entre les deux régions dopées n est manquant.

Cela peut être considéré comme la différence fondamentale entre la disposition interne d'un MOSFET de type à épuisement et de type à amélioration, c'est-à-dire l'absence d'un canal inhérent qui est censé faire partie du dispositif.

On peut voir la couche de SiO2 toujours prévalente, ce qui assure une isolation entre la base métallique de la borne de grille et la région entre le drain et la source. Cependant, ici, il peut être observé debout séparé de la section de matériau de type p.

De la discussion ci-dessus, nous pouvons conclure qu'une disposition interne d'un MOSFET à appauvrissement et à amélioration peut avoir certaines similitudes, à l'exception du canal manquant entre drain / source pour un type d'amélioration de MOSFET.

Fonctionnement et caractéristiques de base

Pour un MOSFET de type amélioration lorsqu'un 0 V est introduit à son VGS, en raison du canal n manquant (qui est connu pour transporter beaucoup de porteuses libres), une sortie de courant est nulle, ce qui est assez différent d'un type d'appauvrissement de MOSFET, ayant ID = IDSS.

Dans une telle situation en raison d'un chemin manquant à travers les bornes drain / source, de grandes quantités de porteurs sous forme d'électrons sont incapables de s'accumuler au drain / source (à cause des régions dopées n).

En appliquant un potentiel positif à VDS, avec VGS réglé à zéro volt et la borne SS court-circuitée avec la borne source, nous trouvons en fait quelques jonctions pn polarisées en inverse entre les régions dopées n et le substrat p pour permettre une conduction notable à travers drainer à la source.

La figure 5.32 montre une condition dans laquelle VDS et VGS sont appliqués avec une certaine tension positive supérieure à 0 V, permettant au drain et à la grille d'être à un potentiel positif par rapport à la source.

Le potentiel positif au niveau de la grille pousse les trous dans le substrat p le long du bord de la couche de SiO2 partant de l'emplacement et pénétrant plus profondément dans les régions du substrat p, comme indiqué sur la figure ci-dessus. Cela se produit à cause des charges similaires qui se repoussent.

Il en résulte la création d'une région d'appauvrissement proche de la couche isolante SiO2 qui est dépourvue de trous.

Malgré cela, les électrons du substrat p qui sont les porteurs minoritaires du matériau sont attirés vers la grille positive et commencent à se rassembler dans la région proche de la surface de la couche de SiO2.

En raison de la propriété d'isolation de la couche de SiO2, les porteurs négatifs permettent aux porteurs négatifs d'être absorbés à la borne de grille.

Lorsque nous augmentons le niveau de VGS, la densité électronique proche de la surface de SiO2 augmente également, jusqu'à ce que finalement la région de type n induite soit capable de permettre une conduction quantifiable à travers le drain / source.

L'amplitude VGS qui provoque une augmentation optimale du courant de drain est appelée tension de seuil, signifié par le symbole VT . Dans les fiches techniques, vous pourrez voir cela comme VGS (Th).

Comme appris ci-dessus, en raison de l'absence d'un canal à VGS = 0, et «amélioré» avec l'application de tension grille-source positive, ce type de MOSFET est connu sous le nom de MOSFET de type amélioration.

Vous constaterez que les MOSFET de type appauvrissement et d'amélioration présentent des régions de type amélioration, mais le terme renforcement est utilisé pour ce dernier car il fonctionne spécifiquement en utilisant un mode de fonctionnement d'amélioration.

Maintenant, lorsque VGS est poussé au-dessus de la valeur de seuil, la concentration des porteurs libres augmentera dans le canal où elle est induite. Cela provoque une augmentation du courant de drain.

D'un autre côté, si nous maintenons le VGS constant et augmentons le niveau VDS (tension drain-source), cela finira par amener le MOSFET à atteindre son point de saturation, comme cela se produirait normalement avec n'importe quel JFET ou un MOSFET d'appauvrissement.

Comme le montre la figure 5.33, le courant de drain ID est nivelé à l'aide d'un processus de pincement, indiqué par le canal plus étroit vers l'extrémité de drain du canal induit.

En appliquant la loi de tension de Kirchhoff aux tensions aux bornes du MOSFET sur la figure 5.33, nous obtenons:

Si VGS est maintenu constant à une valeur spécifique, par exemple 8 V, et VDS est augmenté de 2 à 5 V, la tension VDG par Eq. 5.11 pouvait être vu chuter de -6 à -3 V, et le potentiel de grille devenant de moins en moins positif par rapport à la tension de drain.

Cette réponse empêche les porteurs libres ou les électrons d'être attirés vers cette région du canal induit, ce qui entraîne à son tour une baisse de la largeur effective du canal.

En fin de compte, la largeur du canal diminue jusqu'au point de pincement, atteignant une condition de saturation similaire à ce que nous avons déjà appris dans notre article précédent sur le MOSFET d'épuisement.

Cela signifie que l'augmentation du VDS avec un VGS fixe n'affecte pas le niveau de saturation de l'ID, jusqu'au point où une situation de panne est atteinte.

En regardant la figure 5.34, nous pouvons identifier que pour un MOSFET comme sur la figure 5.33 ayant VGS = 8 V, la saturation a lieu à un niveau VDS de 6 V.Pour être précis, le niveau de saturation VDS est associé au niveau VGS appliqué par:

Sans aucun doute, cela implique donc que lorsque la valeur VT est fixée, l'augmentation du niveau de VGS entraînera proportionnellement des niveaux de saturation plus élevés pour VDS à travers le lieu des niveaux de saturation.

En se référant aux caractéristiques représentées sur la figure ci-dessus, le niveau de VT est de 2 V, ce qui est évident par le fait que le courant de drain est tombé à 0 mA.

Par conséquent, nous pouvons généralement dire:

Lorsque les valeurs VGS sont inférieures au niveau de seuil du MOSFET de type à amélioration, son courant de drain est de 0 mA.

Nous pouvons également clairement voir dans la figure ci-dessus que tant que le VGS est élevé plus haut de VT à 8 V, le niveau de saturation correspondant pour l'ID augmente également du niveau 0 à 10 mA.

De plus, nous pouvons en outre remarquer que l'espace entre les niveaux de VGS augmente avec une augmentation de la valeur de VGS, provoquant des incréments infiniment croissants du courant de drain.

Nous constatons que la valeur du courant de drain est liée à la tension grille-source pour les niveaux VGS supérieurs à VT, via la relation non linéaire suivante:

Le terme qui est montré crochet carré est le terme qui est responsable de la relation non linéaire entre ID et VGS.

Le terme k est une constante et est une fonction de la disposition MOSFET.

Nous pouvons connaître la valeur de cette constante k grâce à l'équation suivante:

où l'ID (activé) et VGD (activé) sont chacun des valeurs dépendant spécifiquement de la caractéristique de l'appareil.

Dans la figure 5.35 suivante, nous trouvons que les caractéristiques de drain et de transfert sont disposées l'une à côté de l'autre pour clarifier le processus de transfert les unes à côté des autres.

Fondamentalement, il est similaire au processus expliqué précédemment pour les MOSFET de type JFET et d'épuisement.

Cependant, dans le cas présent, nous devons nous rappeler que le courant de drain est de 0 mA pour VGS VT.

Ici, l'ID peut voir une quantité notable de courant, qui augmentera comme déterminé par Eq. 5.13.

À noter, tout en définissant les points sur les caractéristiques de transfert à partir des caractéristiques du drain, nous ne considérons que les niveaux de saturation. Cela restreint la région de fonctionnement à des valeurs VDS supérieures aux niveaux de saturation établis par Eq. (5,12).

MOSFET de type à amélioration de canal p

La structure d'un MOSFET de type à amélioration de canal p comme illustré sur la figure 5.37a est juste l'opposé de celle représentée sur la figure 5.31.

Ce qui signifie, maintenant vous trouvez qu'un substrat de type n et des régions dopées p sous les joints de drain et de source.

Les bornes continuent à être telles qu'établies, mais chacune des directions de courant et les polarités de tension sont inversées.

Les caractéristiques du drain peuvent ressembler à celles indiquées sur la figure 5.37c, avec des quantités croissantes de courant provoquées par des amplitudes continuellement plus négatives de VGS.

Les caractéristiques de transfert seraient l'impression de miroir (autour de l'axe ID) de la courbe de transfert de la figure 5.35, ayant l'ID augmentant avec des valeurs de plus en plus négatives de VGS au-dessus de VT, comme illustré sur la figure 5.37b. Les équations (5.11) à (5.14) sont également appropriées pour les dispositifs à canal p.

Les références:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4%AE%E0%A5%89%E0%A4%B8%E0%A4%AB%E0%A5%87%E0%A4%9F

Une paire de: Circuit de détection anti-espion RF - Détecteur de bogues sans fil Suivant: Caractéristiques de transfert